BSIM4 Model Verilog-A Implementation

BSIM4 Model

The Verilog-A hardware description language opens many areas to SPICE users in the field of compact models, allowing manufacturers and universities to study or customize the existing models.

Berkeley BSIM4 model is developed to explicitly address many issues in modeling sub-0.13 microns CMOS technologies and RF high-speed CMOS circuit simulation. Due to its forefront use, BSIM4 was a good candidate for Verilog-A porting.

The Silvaco Verilog-A porting is based on the BSIM4 version 3.0 released on May, 9th 2003. The version 2.6.0.R of SmartSpice Verilog-A interface has been used.

Verilog-A Porting

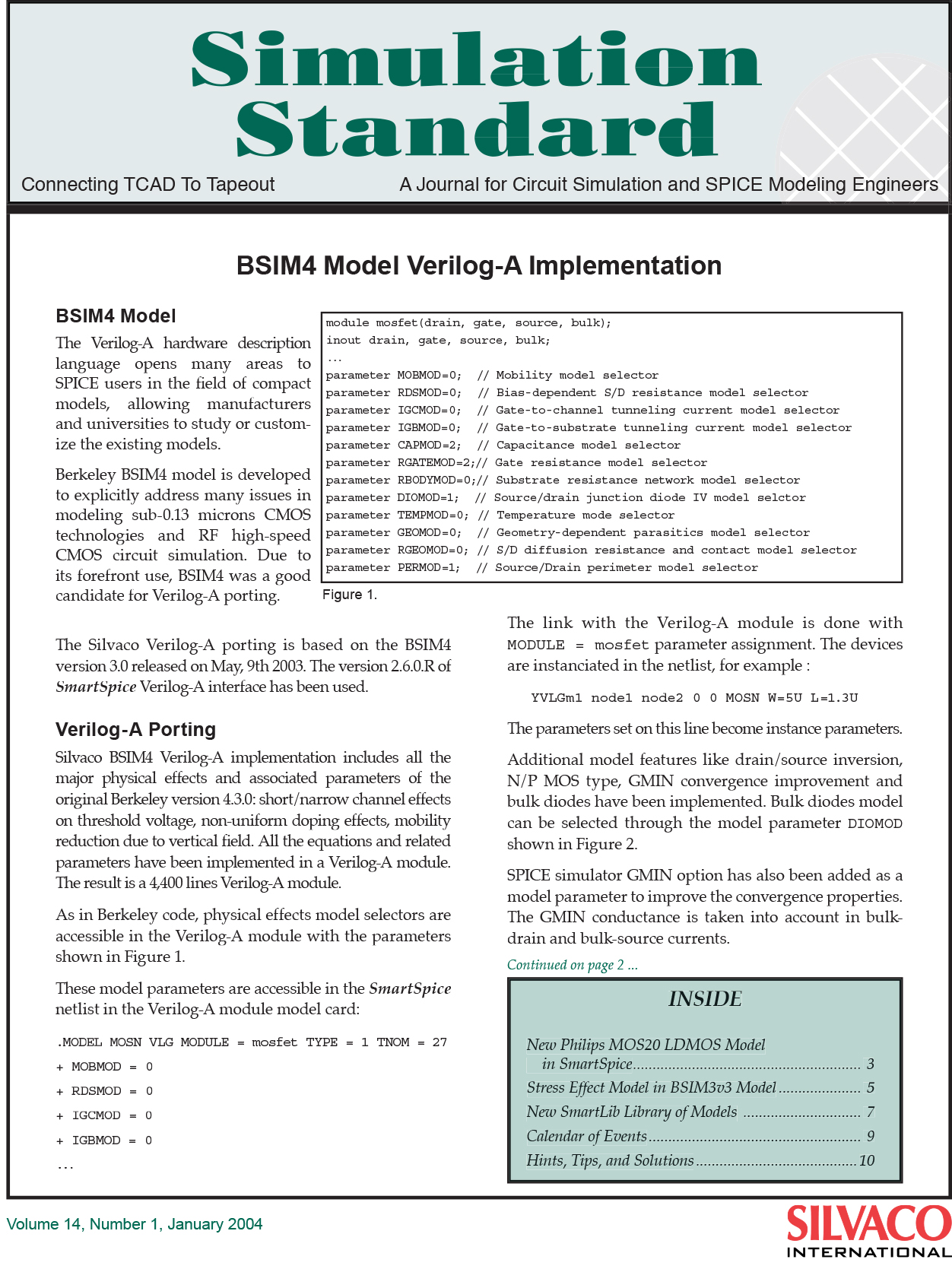

Silvaco BSIM4 Verilog-A implementation includes all the major physical effects and associated parameters of the original Berkeley version 4.3.0: short/narrow channel effects on threshold voltage, non-uniform doping effects, mobility reduction due to vertical field. All the equations and related parameters have been implemented in a Verilog-A module. The result is a 4,400 lines Verilog-A module.