SET Accurate Compact Model for SET-MOSFET Hybrid Circuit Simulation

C. Le Royer*, G. Le Carval*, M. Sanquer**

* CEA-DRT-LETI&CEA/GRE, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France

cyrille.leroyer@cea.fr, gilles.lecarval@cea.fr

** CEA-DRFMC, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France

marc.sanquer@cea.fr

The following article, by Le Royer, C., Le Carval, G., Sanquer, M.: SET Accurate Compact Model for SET-MOSFET Hybrid Circuit Simulation. In: Wachutka, G., Schrag, G. (eds.), Simulation of Semiconductor Processes and Devices 2004. Wien&New York: Springer. 2004 (http://www.springer.at/main/book.jsp?bookID=3-211-22468-8), demonstrates the flexibility of SmartSpice used with its module Verilog-A in the simulations of SET circuits and hybrid SET-MOSFET circuits.

Abstract

Single-Electron Transistors (SETs) [1][2] are attractive candidates for post-CMOS VLSI ICs. Accurate models are also required in order to efficiently design SET circuits and hybrid circuits. We have developed a new physical compact model of SET [3][4], which enables the accurate simulation of SET circuits and hybrid circuits in a SPICE-like environment. We show advanced examples of applications of our approach: simulations of elementary circuits which functionalities have been experimentally demonstrated in the literature [5][6].

1 Introduction

SETs have attracted much attention because of their low power consumption and small size [1][2][7]. Recent works [5][6] show that Single-Electron Transistors could enable innovative functionalities if they are associated with MOSFETs. However Monte-Carlo (MC) simulation [8] is not adapted to the analysis and the optimization of realistic logic circuits with a large number of devices (MOSFETs and SETs).

In this paper, we propose a compact physically based SET model, describing SET characteristics accurately over a wide range of temperature and voltages [4]. Our approach is simpler and more efficient than those presented in the literature [9][10]. Our model has been validated in static and dynamic regimes [4], at both device and logic circuit levels, by comparison with the MC simulator SIMON [8].

2 SET Modeling

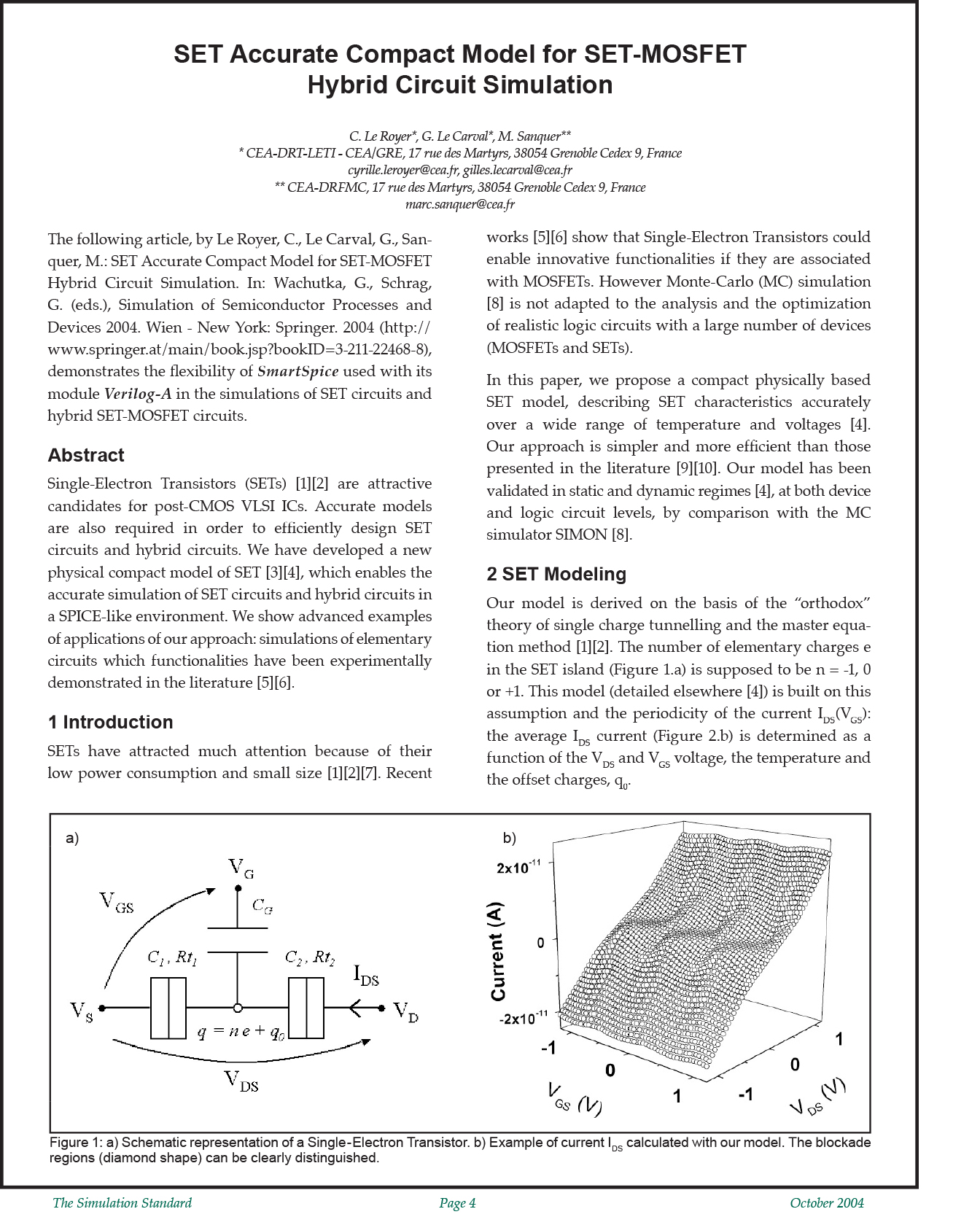

Our model is derived on the basis of the “orthodox” theory of single charge tunnelling and the master equation method [1][2]. The number of elementary charges e in the SET island (Figure 1.a) is supposed to be n = -1, 0 or +1. This model (detailed elsewhere [4]) is built on this assumption and the periodicity of the current IDS(VGS) : the average IDS current (Figure 2.b) is determined as a function of the VDS and VGS voltage, the temperature and the offset charges, q0.