Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

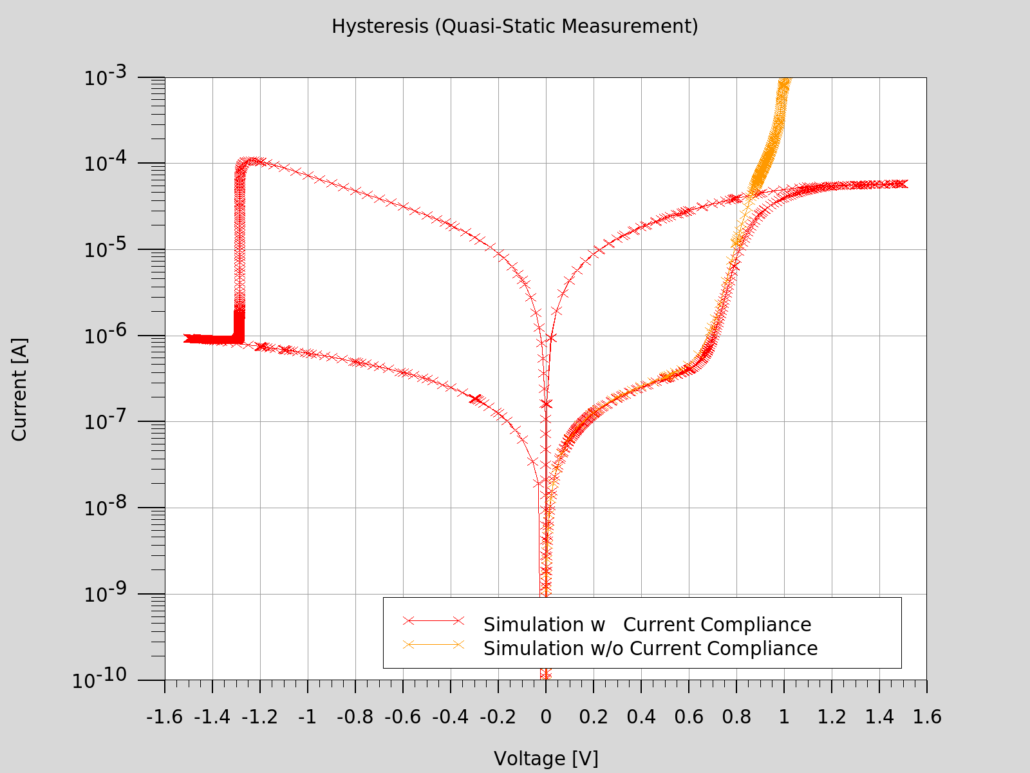

TCAD Mixed-Mode Simulation for GaN Power HEMTs in Unclamped Inductive Switching

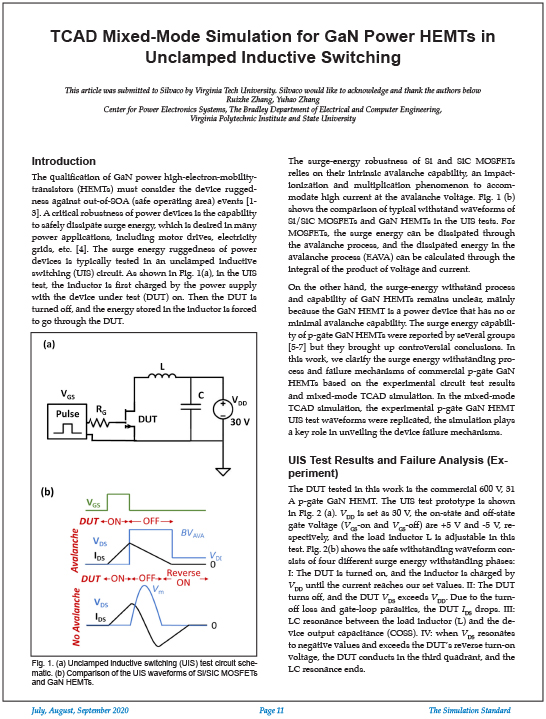

The qualification of GaN power high-electron-mobilitytransistors (HEMTs) must consider the device ruggedness against out-of-SOA (safe operating area) events [1- 3].

Using Victory Process Open Model Interface to Customize Etch Emulation Model – Example

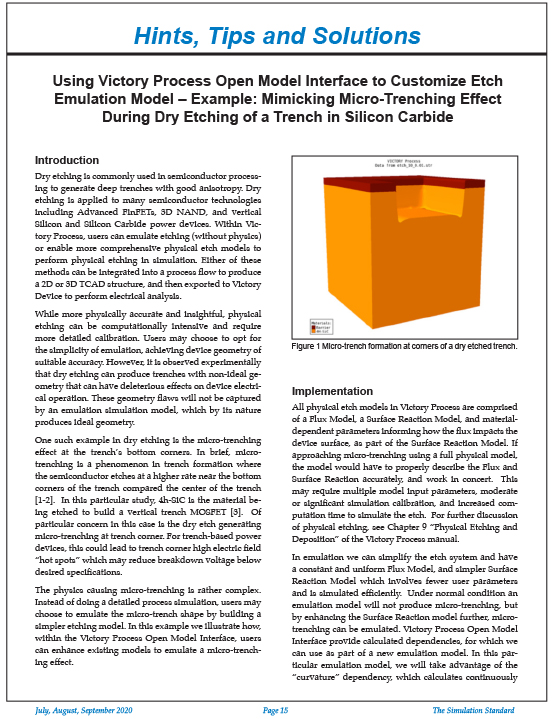

Dry etching is commonly used in semiconductor processing to generate deep trenches with good anisotropy. Dry etching is applied to many semiconductor technologies including Advanced FinFETs, 3D NAND, and vertical Silicon and Silicon Carbide power devices.

2020 TCAD Baseline Release Section 1: Process Simulation – New Features in 2020 Baseline Release

2020 TCAD Baseline Release

Section 1: Process Simulation – New Features in 2020 Baseline Release

2020 TCAD Baseline Release Section 2: Meshing – New Features in 2020 Baseline Release

2020 TCAD Baseline Release

Section 2: Meshing – New Features in 2020 Baseline Release

2020 TCAD Baseline Release – Device Simulation – New Features in 2020 Baseline Release

2020 TCAD Baseline Release Section 3:

Device Simulation – New Features in 2020 Baseline Release

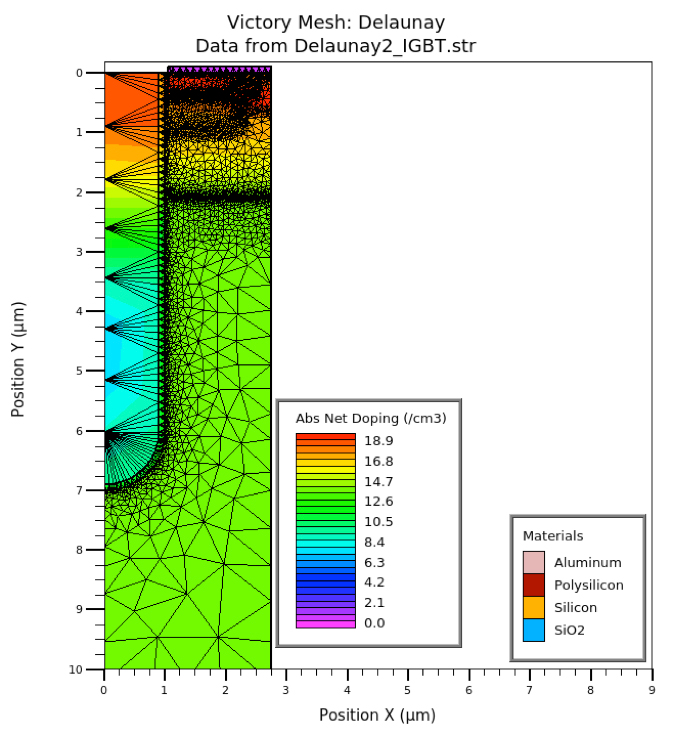

Victory TCAD Suite: How to use it for fast, efficient, and accurate simulation of power semiconductor devices

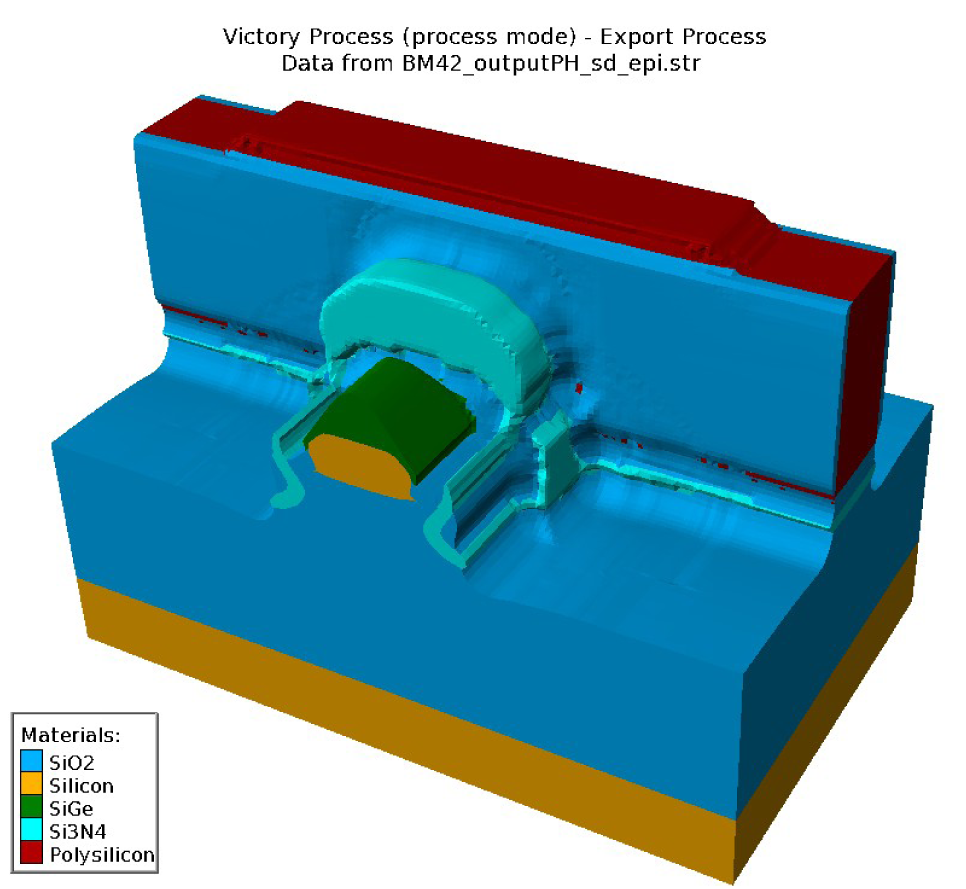

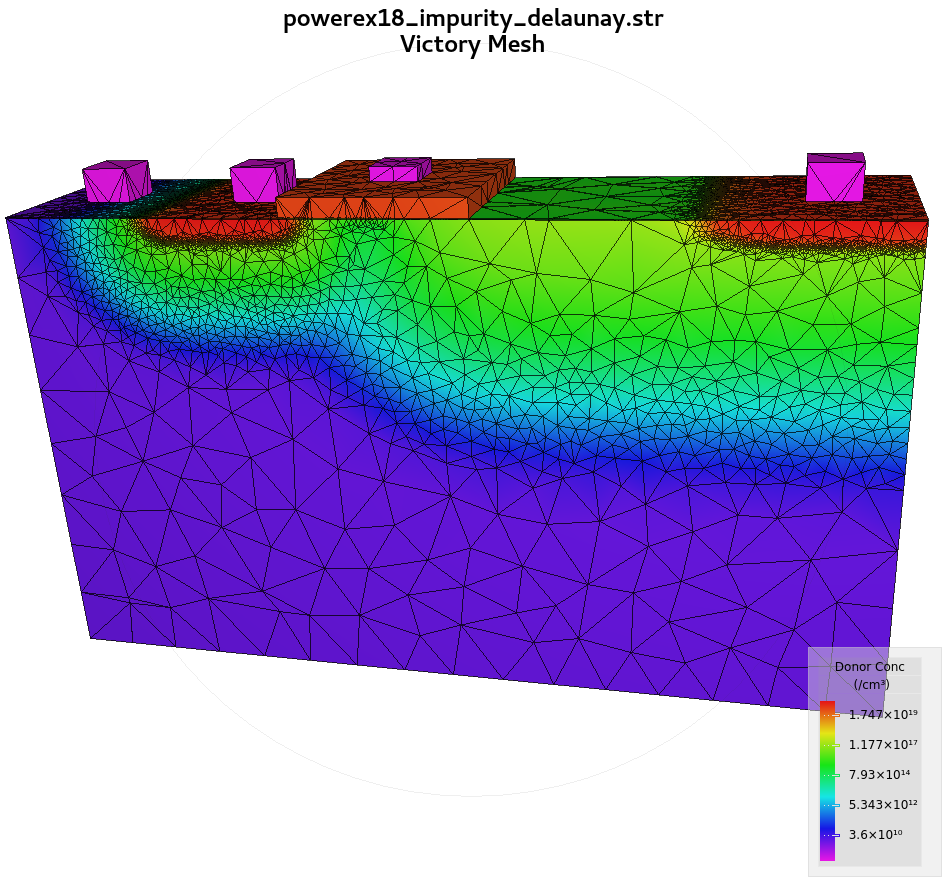

Silvaco TCAD has been used by Tier 1 power device manufactures and designers for decades. The introduction of Victory Process, Victory Mesh, and Victory Device significantly increases the functionality and flexibility of the tool set available to designers. In this article we look at how some of the features of this suite of tools improve the efficiency of the design flow.