Jivaro Pro:寄生参数缩减

为您的SPICE仿真加速,闪电般快速呈现结果

全球多家领先的IDM和半导体设计公司已经采用Jivaro Pro,以解决后版图仿真中日益增加的时间和资源问题。Jivaro Pro使用了专利的寄生缩减数学方法,在降低电路复杂性的同时,还能保持电路的准确性。

Jivaro Pro SPICE仿真加速

Jivaro Pro简介

从65纳米节点到2纳米节点,Jivaro Pro对网表提取和仿真工具都没有要求,可以直接集成到任何设计流程中。与基于规则的和内嵌的寄生参数缩减的方法相比,Jivaro Pro为用户在精确度与缩减程度之间的权衡提供了高度灵活性。为了方便使用,Jivaro Pro提供自动模式功能,能够自动适应您的设计。还有超过30个可调参数,广泛控制仿真的速度和准确性。

使用Jivaro Pro,用户能够为所有应用提供单一解决方案,从容应对流程和设计类型等方面的挑战,让寄生参数缩减尽在掌握。

有针对性的缩减:区块或网络

优势

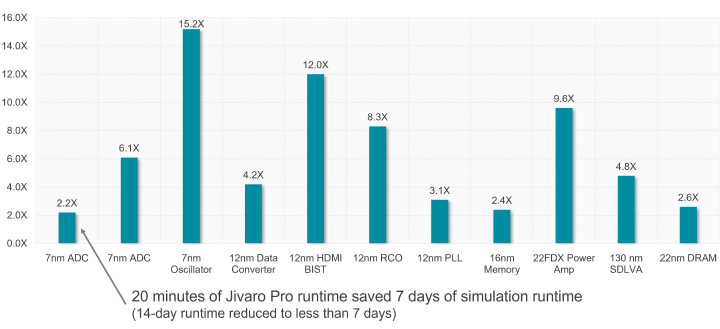

- 高达15倍的布局后SPICE仿真加速

- 轻松应用于现有流程中

- 实现运行大型或以前不可能的仿真

- 在仿真中考虑功耗网络和金属填充,以提高准确性

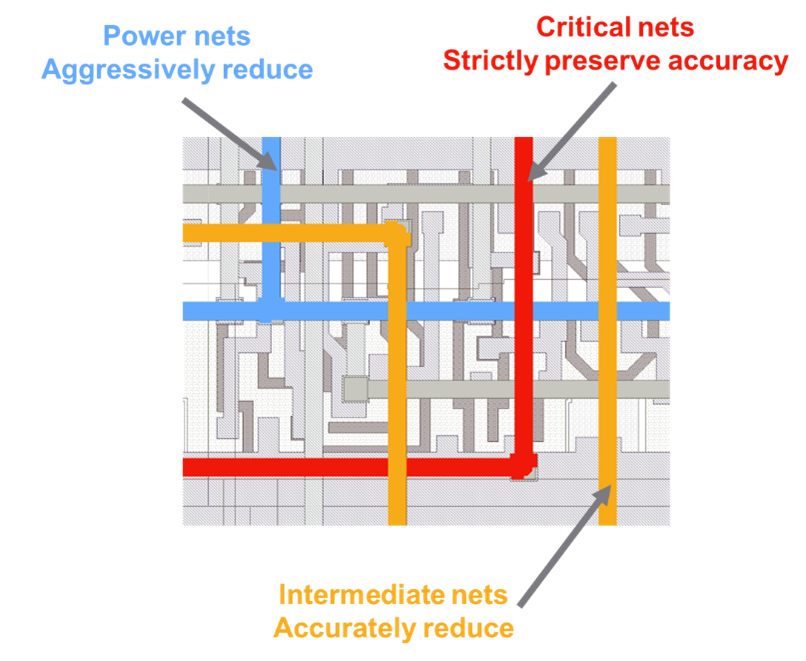

- 可定制的寄生缩减策略,灵活满足您的目标

- 通过更多仿真提高覆盖范围

- 最小化所需的计算资源(即CPU和内存配置)

功能特性

- 支持R、RC、RCC、RLC、RLCK和受控源

- 支持DSPF、SPEF、SPICE3、HSPICE®、SPECTRE®、Calibre® View和OA数据库

- 缩减温度相关的寄生网表和多角提取的网表

- 可有选择地缩减层次结构中的网络、子电路或路径

- 直观的配置和分析界面

- Jivaro Pro与所有主流的EDA工具兼容