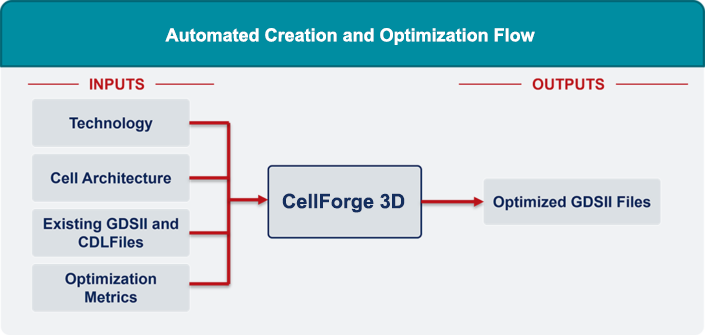

CellForge 3D 流程

主要特点

- 支持10nm以下FinFET

- 集成的布局布线引擎,可创建符合设计要求的版图

- 兼容多重图形规则、切割规则或任何其他复杂的FinFET工艺规则

- 支持高级工艺技术,包括上下相关的间距和包孔规则、首选形状模式、自对准双图形(SADP)和内部互连

- 可扩展的并行处理以提高处理量

- 同时生成多个布局选项

- 与领先的第三方DRC、LVS和LPE工具集成,确保高质量的签核版图,且对现有流程的影响非常小

- 灵活设置工艺技术和代工厂设计规则,超快速生成DRC合规版图

主要优势

- 显著提高生产力

- 消除或显著减少版图设计的手动工作

- 快速的设计周转时间,一天完成库设计

- 支持对不同维度的进一步探索,包括单元的设计结构、设计规则、设计尺寸、不同设计高度和DFM规则

- 版图一致性

- 复用原理图,缩短设计时间

- PDK自动更新

On-Chip Variation and the Sign-off Timing Flow: An Industry Perspective

Nanometer Library Characterization: Challenges and Solutions

Standard Cell Layout Migration and Optimization