EKV MOSFET Model Version 2.6 Now Available in SmartSpice and UTMOST III

Silvaco now offers the EKV (ENZ, KRUMMENACHER, VITTOZ) MOSFET model version 2.6 originally developed in EPFL ("Ecole Polytechnique Federale de Lausanne" - Switzerland), as part of the SmartLib product-independent model library. This model is available within SmartSpice and UTMOST as level 44.

BSIM3v3.2 Model Released in SmartSpice and UTMOST III

The latest Berkeley BSIM3v3.2 model of June 16 1998 is now available in the SmartSpice 1.5.5 release.

Two BSIM3v3.2 implementations are supported in SmartSpice and UTMOST III.

HINTS AND TIPS – June 1998

Q: Can I draw tangents to circles in EXPERT?

A: Expert supports several options for drawing sophisticated shapes. There are three ways to accomplish this task.

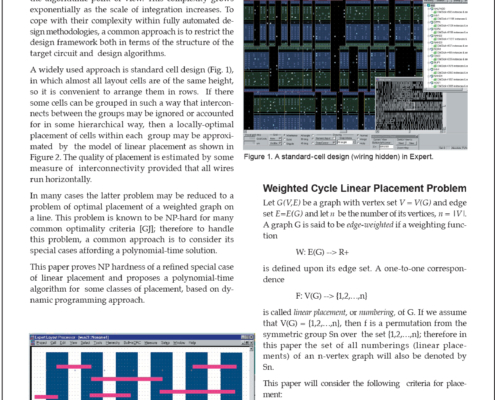

Optimum Standard Cell Layout Using Weighted Cycle Linear Placement

Placement and routing problems for integrated circuits are inherently interrelated and extremely complex from the algorithmic point of view. This complexity grows exponentially as the scale of integration increases.

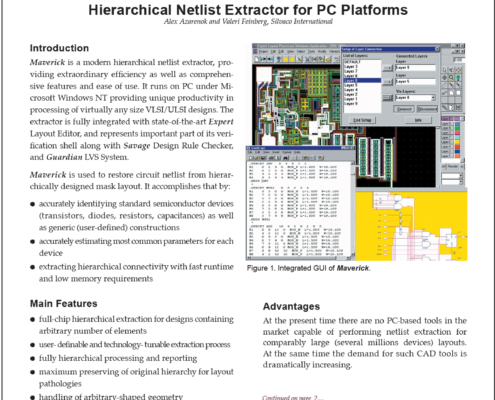

Maverick: Hierarchical Netlist Extractor for PC Platforms

Maverick is a modern hierarchical netlist extractor, providing extraordinary efficiency as well as comprehensive features and ease of use. It runs on PC under Microsoft Windows NT providing unique productivity in processing of virtually any size VLSI/ULSI designs.

HINTS AND TIPS – May 1998

How can anti-reflective coatings be modeled when simulating photodetectors in ATLAS/Luminous? How can detection efficiency be plotted?

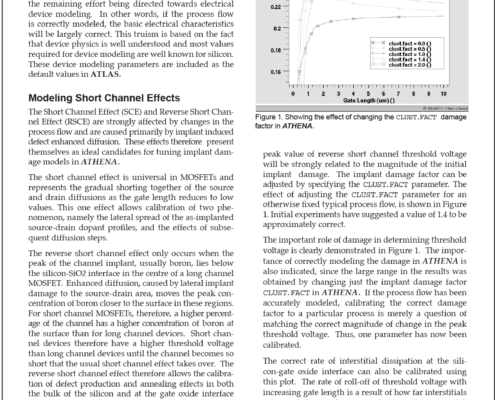

Calibrating Reverse Short Channel Effects in MOSFETs

This article focuses on the effects of process and modeling parameters on device electrical characteristics and uses the threshold voltage versus gate length of a n-MOSFET as an illustration.

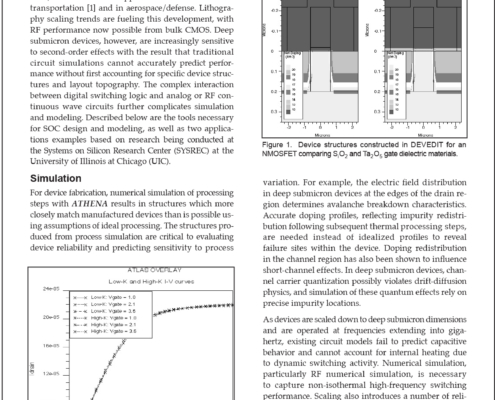

Low-Power Systems-on-a-Chip CAD

Mixed-signal systems-on-a-chip (SOC) integration of digital, analog, RF, and power components is emerging to meet demands for low-power, highly integrated systems in portable computing, wireless communications, and multimedia.

Ultra-Fast Device Simulation with Monte Carlo Tuned Transport Models in FastBlaze

FastBlaze is a fast physical device simulator for MESFETs and HEMTs optimized to provide interactive TCAD for modern III-V FET devices. It incorporates device-specific techniques to allow 1000x to 10000x simulation speeds compared to conventional device simulation.

HINTS & TIPS – April 1998

Q. What is the typical method of measuring flicker noise using S3245A Noise Amplifier?