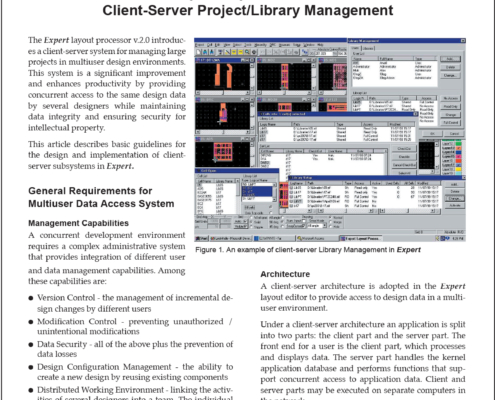

Expert Expanded with Client-Server Project/Library Management

The Expert layout processor v.2.0 introduces a client-server system for managing large projects in multiuser design environments. This system is a significant improvement and enhances productivity by providing concurrent access to the same design data by several designers while maintaining data integrity and ensuring security for intellectual property.

HINTS & TIPS – November 1998

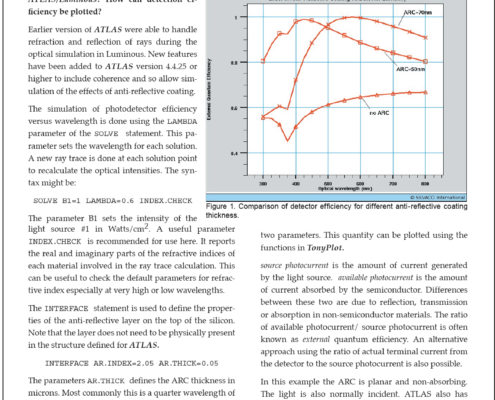

Q: How can anti-reflective coatings be modeled when simulating photodetectors in ATLAS/Luminous? How can detection efficiency be plotted?A: Earlier version of ATLAS were able to handle refraction and reflection of rays during the optical simulation in Luminous.

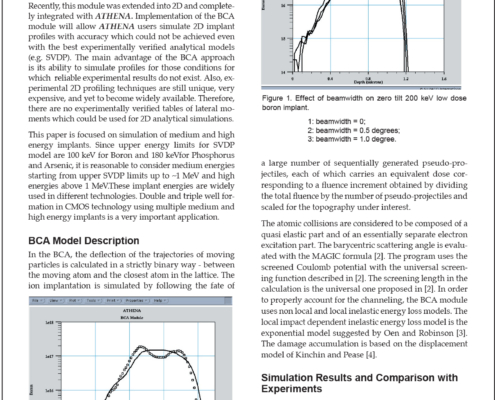

New Model for High Energy Implants in ATHENA

In our earlier paper [1] a new Binary Collision Approximation (BCA) module was described. It was shown that models and algorithms implemented into the BCA model allow to accurately predict implant profiles with significant channeling as well as the dose and screen oxide thickness dependencies for relatively low implant energies.

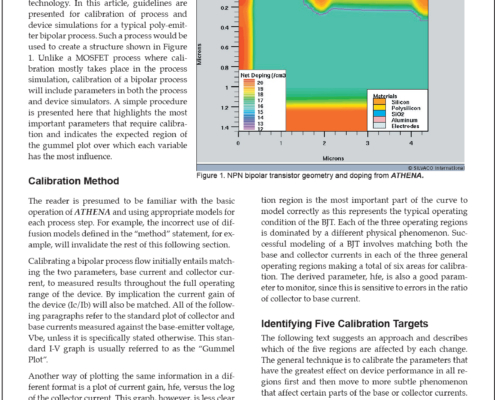

Calibrating a Typical Bipolar Process Flow

A common request from TCAD (Technology Computer Aided Design) users is advise on how to calibrate the process flow and device simulator to a particular technology. In this article, guidelines are presented for calibration of process and device simulations for a typical poly-emitter bipolar process.

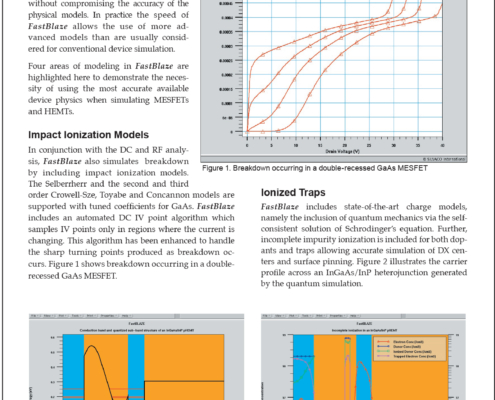

Accurate, High Speed Physics in FastBlaze

FastBlaze uses novel device simulation techniques to simulate typical MESFET and HEMT characteristics in less than a minute. To be a truly useful engineering tool this extremely high speed must be achieved without compromising the accuracy of the physical models.

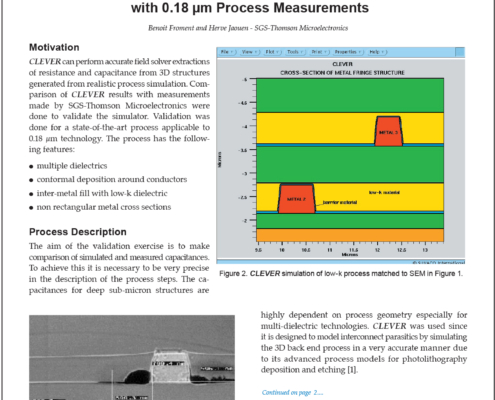

Validation of CLEVER Interconnect Parasitics with 0.18 µm Process Measurements Benoit Froment and Herve Jaouen – SGS-Thomson Microelectronics

CLEVER can perform accurate field solver extractions of resistance and capacitance from 3D structures generated from realistic process simulation. Comparison of CLEVER results with measurements made by SGS-Thomson Microelectronics were done to validate the simulator.

HINTS & TIPS – October 1998

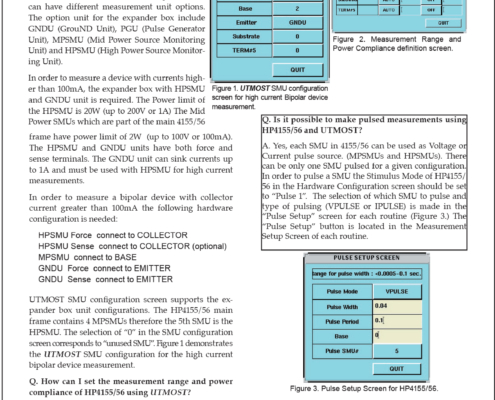

The HP4155/56 DC Analyzer can be configured with SMU and Pulse Generator expander box frame called HP41501A. The expander box can have different measurement unit options.

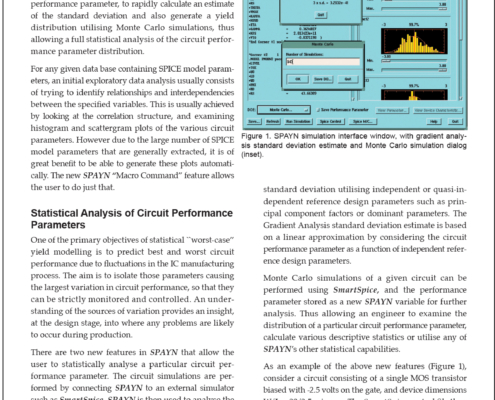

SPAYN Recent Developments

An important aspect of statistical process control in IC production is the ability to predict circuit performance variation in the manufacturing process. Two new features in SPAYN allow the user, for a particular circuit performance parameter, to rapidly calculate an estimate of the standard deviation and also generate a yield distribution utilising Monte Carlo simulations, thus allowing a full statistical analysis of the circuit performance parameter distribution.

Scholar

The debut of Silvaco's new schematic editor, Scholar, is drawing closer. Scholar is a sophisticated design tool which derives its power and flexibility from the fact that it is built on top of the general purpose circuit database.

PHILIPS Model 9

In collaboration with STMicroelectronics Central R&D at Crolles (France), a new routine has been developed in UTMOST III to provide a complete solution for MOS Philips Model 9 parameter extraction. This methodology[1] is based on the local optimization method; we can determine a limited set of 18 parameters (so called miniset) to describe the electrical behavior of each device, considering it as the reference device.