Generation of III-Nitride Transport Parameters with Mocasim

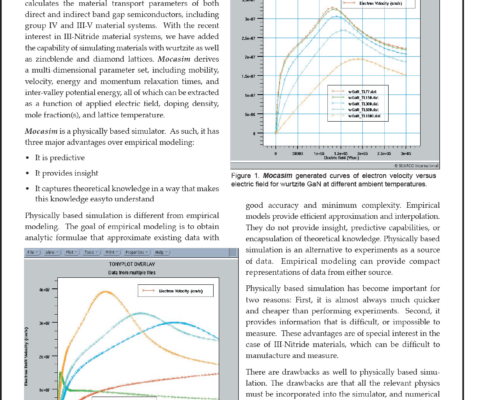

Mocasim is an advanced three-valley Monte Carlo simulator designed to generate the transport parameters used in Silvaco’s physical device simulators. It accurately calculates the material transport parameters of both direct and indirect band gap semiconductors, including group IV and III-V material systems. With the recent interest in III-Nitride material systems, we have added the capability of simulating materials with wurtzite as well as zincblende and diamond lattices. Mocasim derives a multi-dimensional parameter set, including mobility, velocity, energy and momentum relaxation times, and inter-valley potential energy, all of which can be extracted as a function of applied electric field, doping density, mole fraction(s), and lattice temperature.

EXACT Worksheet Utility to View Variables and Data

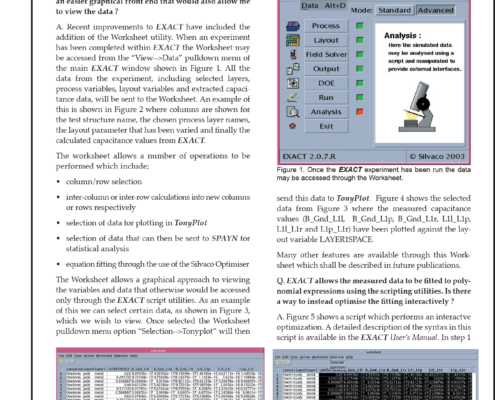

Q: EXACT has powerful scripting utilities for manipulating the final capacitance data and variables but is there an easier graphical front end that would also allow me to view the data?

HiSIM V1.2 Model Parameter Extraction with UTMOST-III

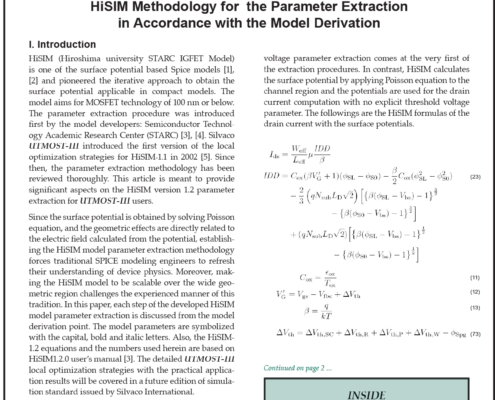

HiSIM (Hiroshima university STARC IGFET Model) is one of the surface potential based Spice models [1], [2] and pioneered the iterative approach to obtain the surface potential applicable in compact models. The model aims for MOSFET technology of 100 nm or below. The parameter extraction procedure was introduced first by the model developers: Semiconductor Technology Academic Research Center (STARC) [3], [4]. Silvaco UTMOST-III introduced the first version of the local optimization strategies for HiSIM-1.1 in 2002 [5]. Since then, the parameter extraction methodology has been reviewed thoroughly. This article is meant to provide significant aspects on the HiSIM version 1.2 parameter extraction for UTMOST-III users.

Shallow-Trench-Isolation (STI) Effects in BSIM4 and HiSIM MOSFET Models in SmartSpice & UTMOST-III

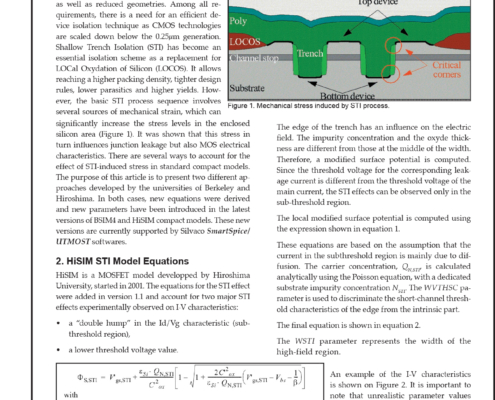

There are several ways to account for the effect of STI-induced stress in standard compact models. The purpose of this article is to present two different approaches developed by the universities of Berkeley and Hiroshima. In both cases, new equations were derived and new parameters have been introduced in the latest versions of BSIM4 and HiSIM compact models. These new versions are currently supported by Silvaco SmartSpice/UTMOST softwares.

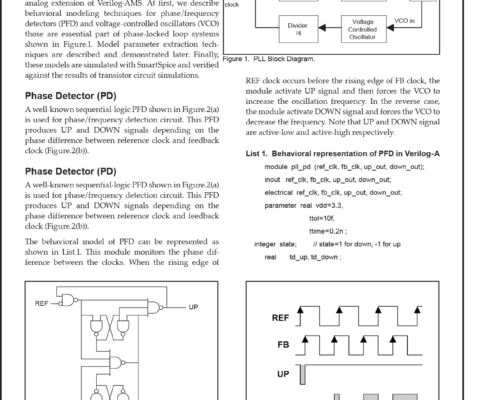

Behavioral Modeling of PLL Using Verilog-A with SmartSpice

In this article, we describe practical behavioral modeling for highly non-linear circuits using Verilog-A, which is analog extension of Verilog-AMS. At first, we describe behavioral modeling techniques for phase/frequency detectors (PFD) and voltage-controlled oscillators (VCO) those are essential part of phase-locked loop systems shown in Figure.1. Model parameter extraction techniques are described and demonstrated later. Finally, these models are simulated with SmartSpice and verified against the results of transistor circuit simulations.

Using Binned Device Models with SmartSpice

Q. My simulation fails because SmartSpice cannot find a binned model, what does this mean?

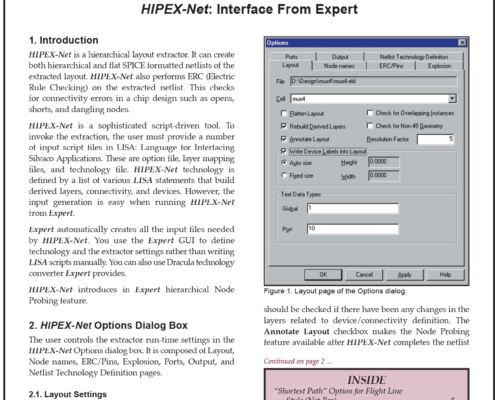

HIPEX-Net: Hierarchical Layout Extractor for Expert Editor

HIPEX-Net is a hierarchical layout extractor. It can create both hierarchical and flat SPICE formatted netlists of the extracted layout. HIPEX-Net also performs ERC (Electric Rule Checking) on the extracted netlist. This checks for connectivity errors in a chip design such as opens, shorts, and dangling nodes.

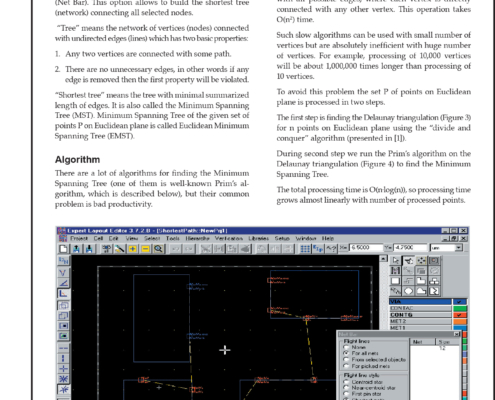

“Shortest Path” Option for Flight Line Style (Net Bar)

There is the recent improvement in Expert Layout Editor, the “Shortest path” option was added to Flight line styles (Net Bar). This option allows to build the shortest tree (network) connecting all selected nodes.

Expert Layout Editor Recent Improvements: Over-the-Point Drawing of Orthogonal Shapes

This article presents an overview of new features added to Silvaco's Expert layout editor. Silvaco has taken a careful look at the real-world obstacles faced daily by semiconductor layout designers and design engineers. Silvaco has augmented Expert with features that dramatically increase flexibility and also help to reduce constraint violations and other roadblocks inherent to complex layout design.

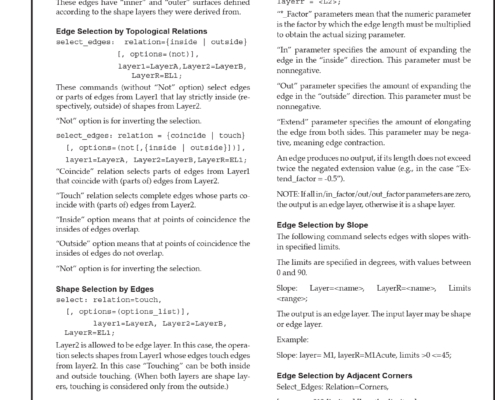

Guardian DRC Edge Layer Operations

Recent versions of Guardian DRC introduce operations that involve edge layers, either on input or on output. An edge layer is a layer that contains line segments that are edges or parts of edges of shapes from other layers. These edges have "inner" and "outer" surfaces defined according to the shape layers they were derived from.