SmartSpice Pro FastSPICE Simulator

SmartSpice Pro는 SRAM 및 TFT기반의 디스플레이 설계에서 뛰어난 성능을 제공합니다. 독자적인 고속 SPICE 알고리즘은 수백만 규모의 메모리 및 디스플레이 회로에 매우 빠르고 정확한 SPICE 시뮬레이션을 제공합니다. SmartSpice Pro는 업계 표준 SmartSpice Analog Simulator와 통합되어 최대 효율성을 제공합니다. 고급 멀티-레이트 이벤트-기반 시뮬레이션 기술은 과도 영역의 회로 검증에 최적의 기능과 유연성을 제공합니다.

특징

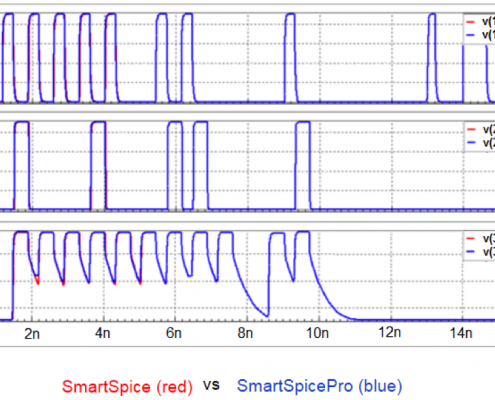

- 고급 멀티-레이트 이벤트 기반 시뮬레이션 방법을 사용함으로써 고정밀의 시뮬레이션 결과 제공

- 고속 병렬 리니어 솔버 사용

- FinFET, PSP, TFT, BSIMSOI, HiSIM 등 고급 소자 모델 지원

- Verilog-A 모델 지원

- TMI 지원

- HSPICE 및 SPECTRE 디바이스 모델과 높은 호환성

- 설계자에 맞춘 포스트 프로세스 기능을 풍부하게 제공

장점

- 기존 SPICE 시뮬레이션 알고리즘을 탑재하여 고정밀도 실현

- 회로의 활성(active) 파티션과 잠재적인(latent) 파티션간 통신에 이벤트 기반의 기술 사용

- 일시적인 다중 속도 시뮬레이션 방식 도입

- 적응 타임 스탭 제어 알고리즘 및 이산화 타임 그리드 매핑 제공

적용

- SRAM 및 TFT 기반의 디스플레이 회로에서 차별화된 시뮬레이션 속도 실현

- 여러 파티션의 통합 알고리즘 제공

- 회로의 선형 RCL 클러스터의 검출 및 활용

- 디지털 애플리케이션 및 아날로그 애플리케이션에 최적

모델

- 분석적 소자 모델: FinFET, BSIM3v3, BSIM4, BSIMSOI, TFT, HiSIM, PSP 등

- Verilog-A 모델 지원

- TMI 지원

- BSIM3v3 및 BSIM4 모델에 대한 룩업 테이블 지원

- HSPICE 및 SPECTRE 모델과 호환되는 모델

시뮬레이션 제어

- DC 동작점 및 과도 분석 지원

- 파티션 동작, 지연 시간 및 커플링 제어 지원

- 이벤트로 동작하는 시뮬레이션에 대해 제어 메커니즘 제공

- 파티션에 대한 정확성을 제어하기 위한 수단 제공

- 전체적인 정확성 및 성능 제어를 위한 구성 (매크로) 옵션 세트 제공

Viso를 활용한 기생 문제의 조사, 분석 및 해결

Si, GaN, SiC 기술에 대한 전력 소자 SPICE 모델링

SmartSpice를 활용하여 최신 TFT 기반 플랫 패널 설계

Utmost IV를 활용한 소자 모델링의 최신 기술

실바코 플로우를 활용한 FPD 및 검출기의 픽셀 어레이 설계 및 시뮬레이션