Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

LISA Powerful Script language for Expert

This article introduces the LISA (Language for Interfacing Silvaco Applications) command language and gives an overview of LISA features.

Expert Expanded with Client-Server Project/Library Management

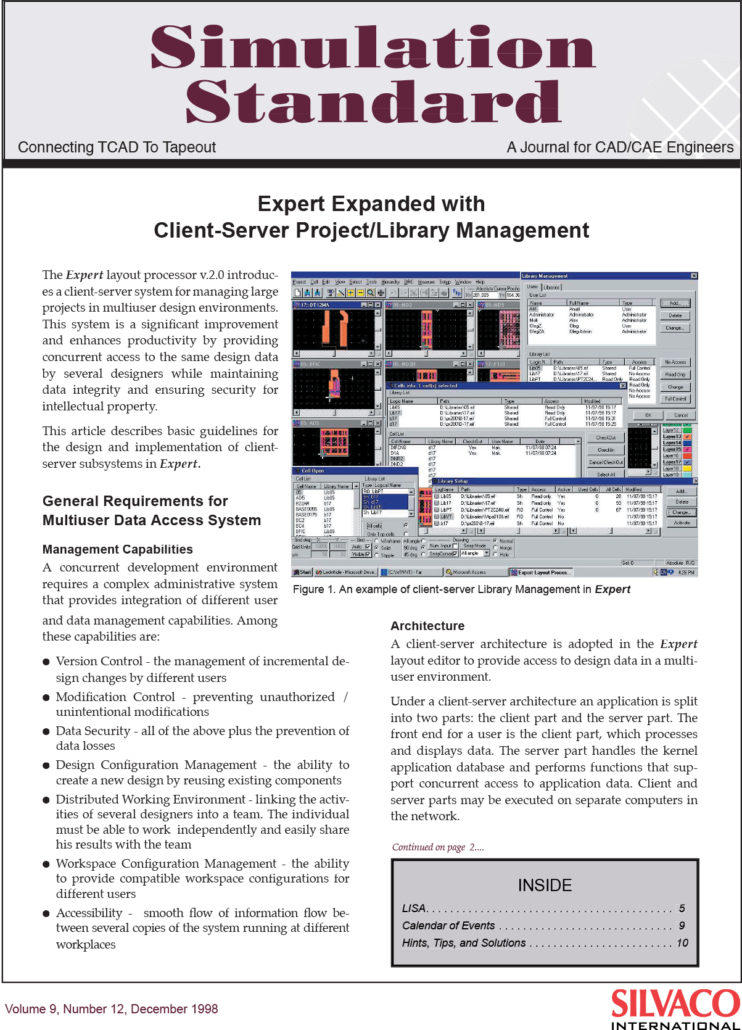

The Expert layout processor v.2.0 introduces a client-server system for managing large projects in multiuser design environments. This system is a significant improvement and enhances productivity by providing concurrent access to the same design data by several designers while maintaining data integrity and ensuring security for intellectual property.

HINTS & TIPS – November 1998

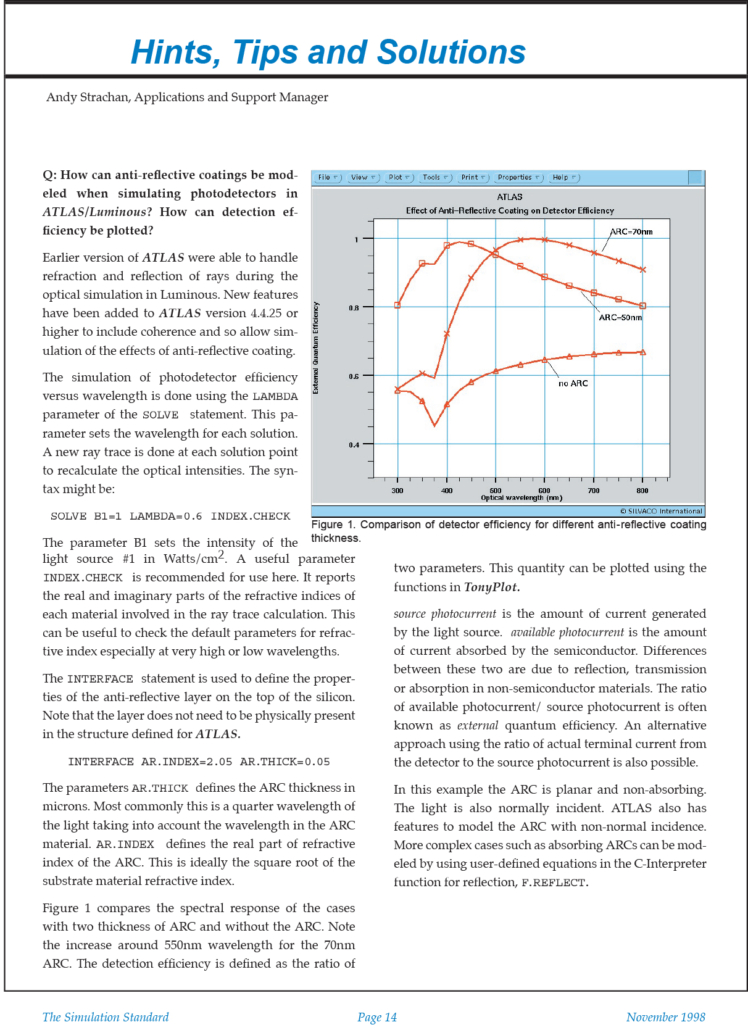

Q: How can anti-reflective coatings be modeled when simulating photodetectors in ATLAS/Luminous? How can detection efficiency be plotted?A: Earlier version of ATLAS were able to handle refraction and reflection of rays during the optical simulation in Luminous.

New Model for High Energy Implants in ATHENA

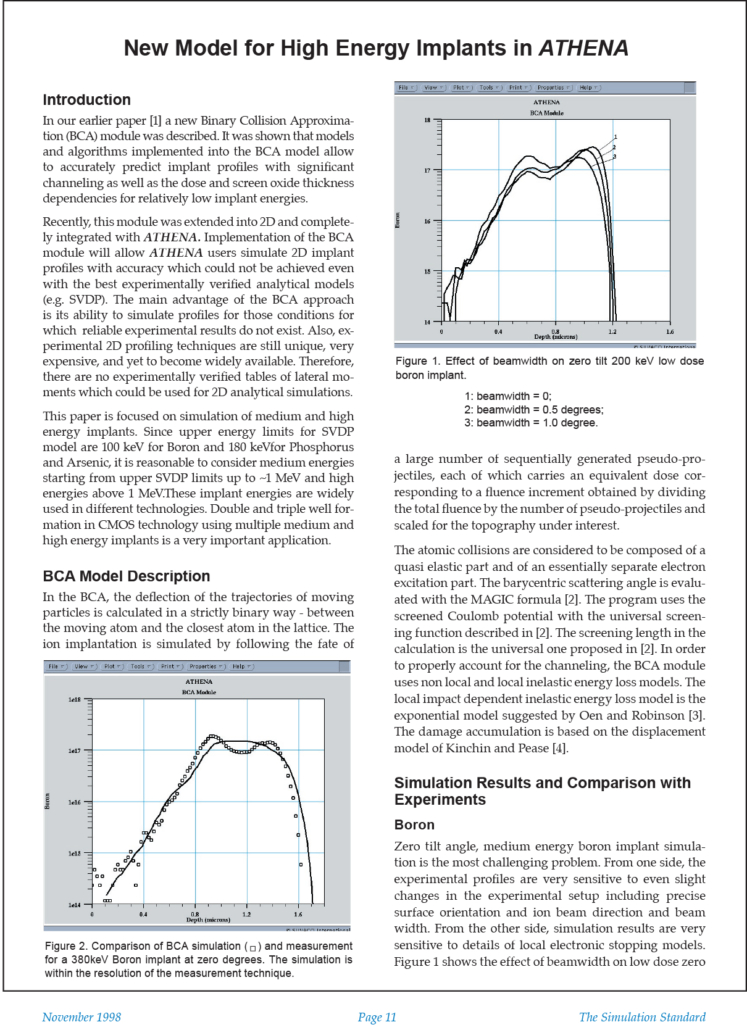

In our earlier paper [1] a new Binary Collision Approximation (BCA) module was described. It was shown that models and algorithms implemented into the BCA model allow to accurately predict implant profiles with significant channeling as well as the dose and screen oxide thickness dependencies for relatively low implant energies.

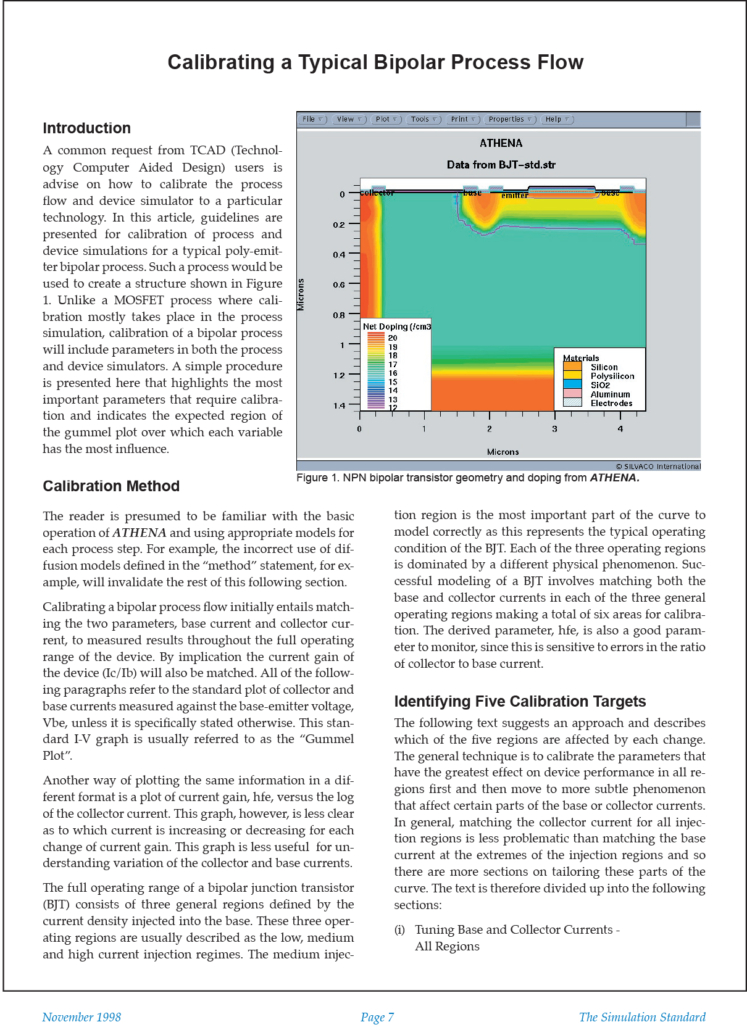

Calibrating a Typical Bipolar Process Flow

A common request from TCAD (Technology Computer Aided Design) users is advise on how to calibrate the process flow and device simulator to a particular technology. In this article, guidelines are presented for calibration of process and device simulations for a typical poly-emitter bipolar process.

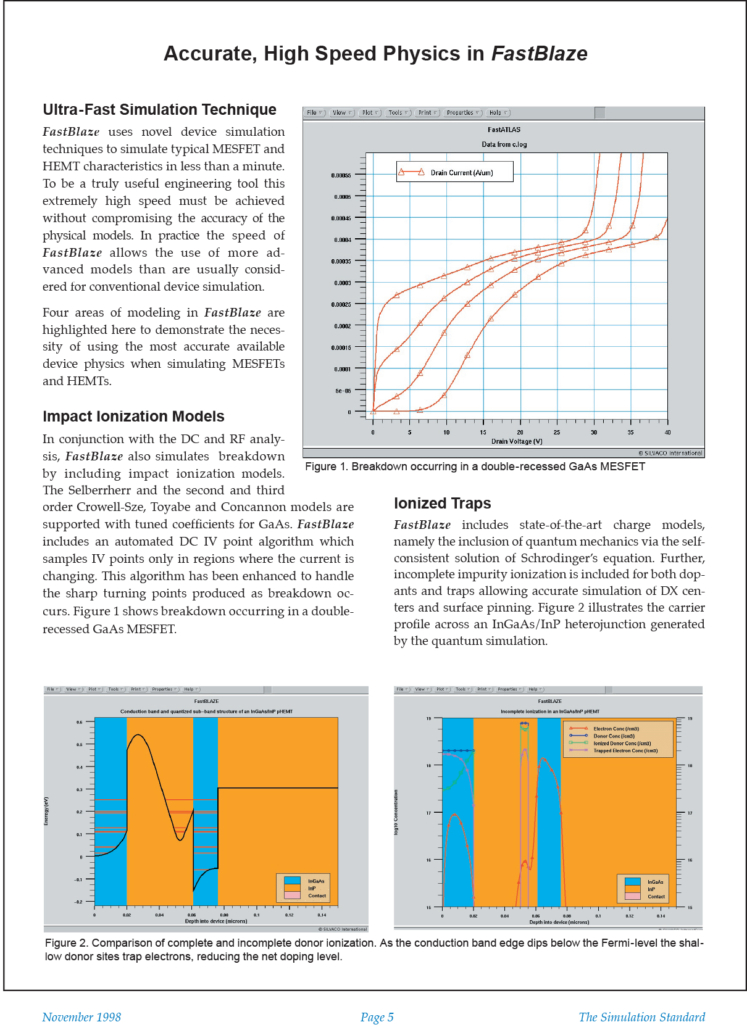

Accurate, High Speed Physics in FastBlaze

FastBlaze uses novel device simulation techniques to simulate typical MESFET and HEMT characteristics in less than a minute. To be a truly useful engineering tool this extremely high speed must be achieved without compromising the accuracy of the physical models.