Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

Expert’s Application Programming Interface (Expert API)

Expert API is intended for customizing and extending the existing software functionality by functions written by the users of Expert using C/C++.

Add Custom Commands to Expert’s Menu

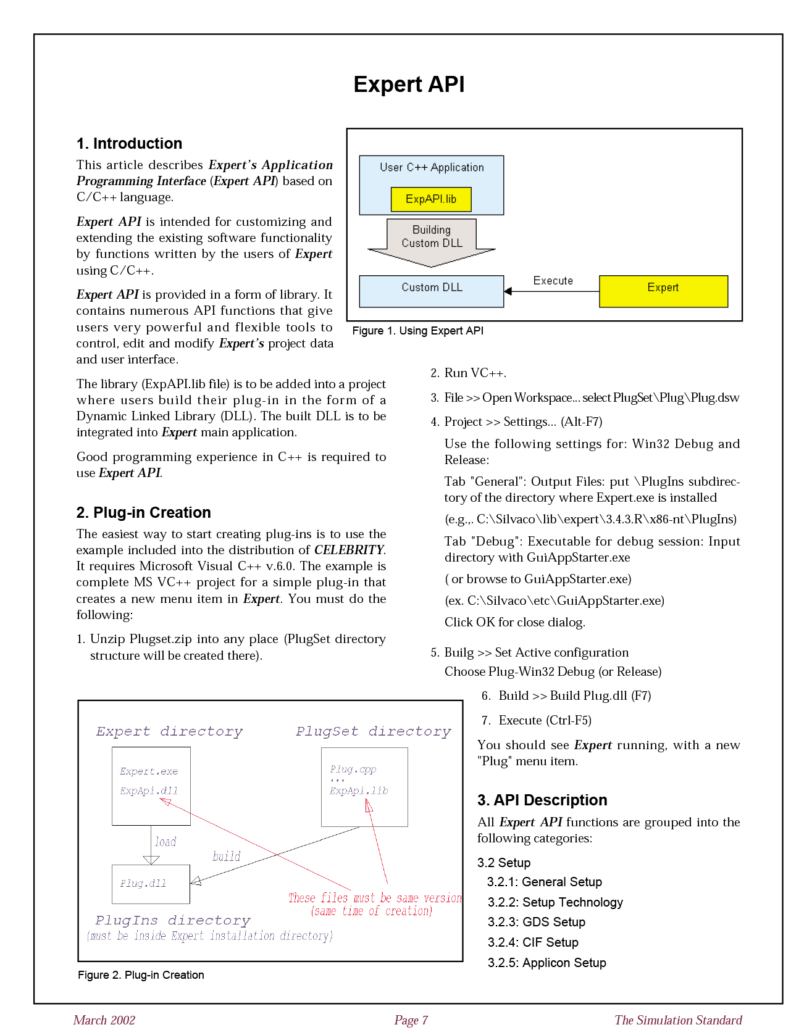

A simple way to add custom commands to Expert's menu is implemented. It is possible to add menu items that execute xi-commands or procedures. To do this, you must put a file named 'custom.mnu' with syntax described below into Expert's executable directory and start (or restart) Expert.

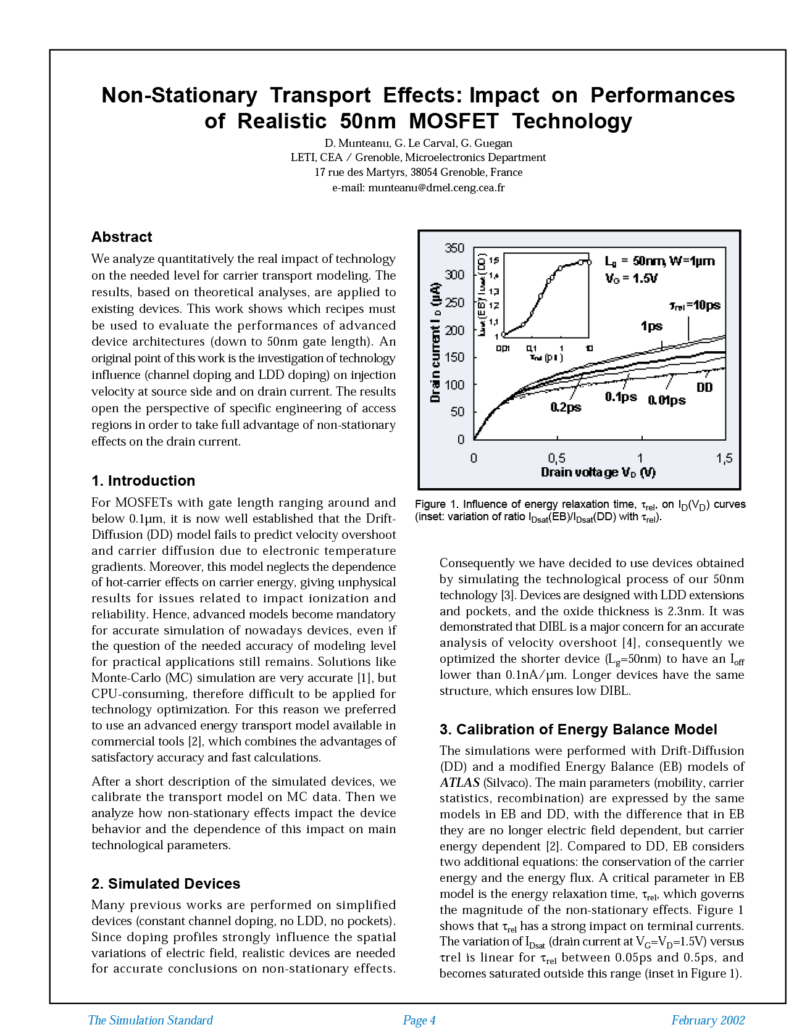

Non-Stationary Transport Effects: Impact on Performances of Realistic 50nm MOSFET Technology

We analyze quantitatively the real impact of technology on the needed level for carrier transport modeling. The results, based on theoretical analyses, are applied to existing devices. This work shows which recipes must be used to evaluate the performances of advanced device architectures (down to 50nm gate length).

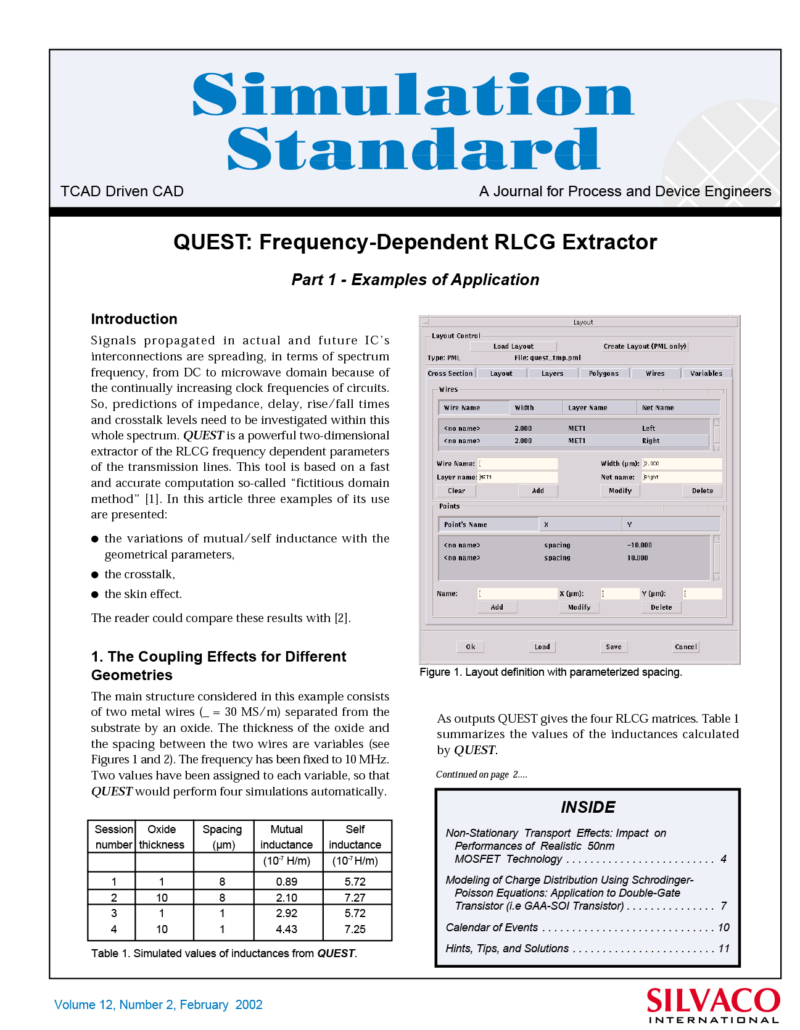

QUEST: Frequency-Dependent RLCG Extractor

Signals propagated in actual and future IC's interconnections are spreading, in terms of spectrum frequency, from DC to microwave domain because of the continually increasing clock frequencies of circuits. So, predictions of impedance, delay, rise/fall times and crosstalk levels need to be investigated within this whole spectrum. QUEST is a powerful two-dimensional extractor of the RLCG frequency dependent parameters of the transmission lines.

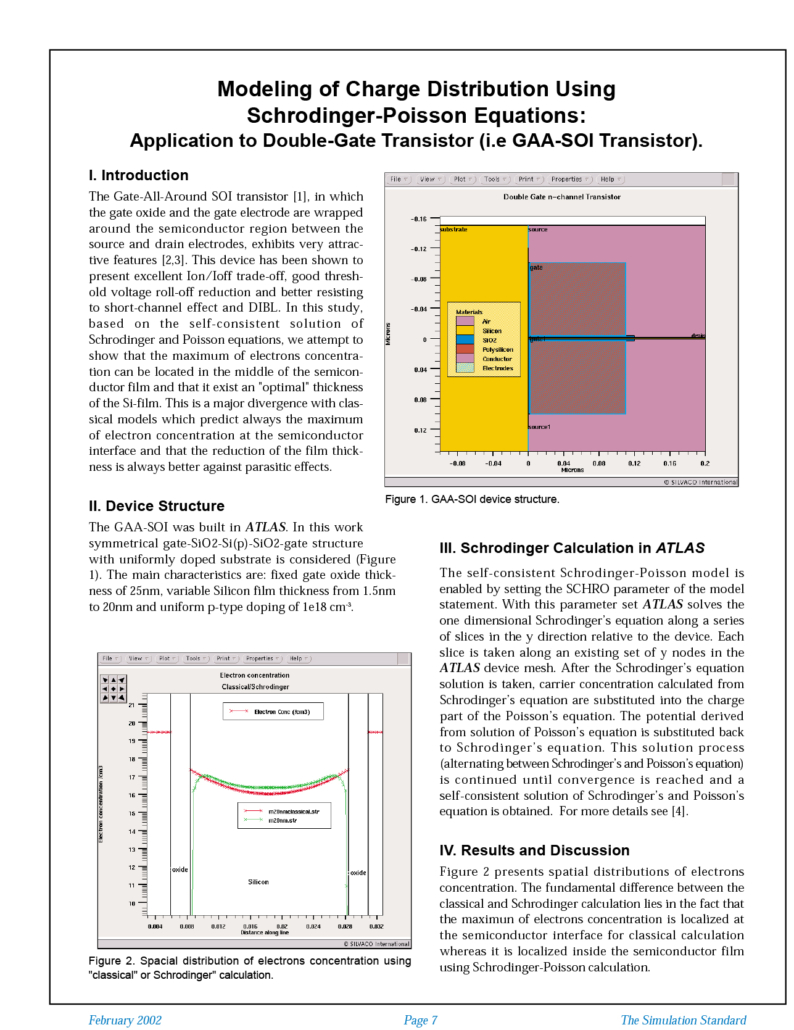

Modeling of Charge Distribution Using Schrodinger-Poisson Equations: Application to Double-Gate GAA-SOI Transistor

The Gate-All-Around SOI transistor [1], in which the gate oxide and the gate electrode are wrapped around the semiconductor region between the source and drain electrodes, exhibits very attractive features [2,3]. This device has been shown to present excellent Ion/Ioff trade-off, good threshold voltage roll-off reduction and better resisting to short-channel effect and DIBL. In this study, based on the self-consistent solution of Schrodinger and Poisson equations, we attempt to show that the maximum of electrons concentration can be located in the middle of the semiconductor film and that there exists

an "optimal" thickness of the Si-film.