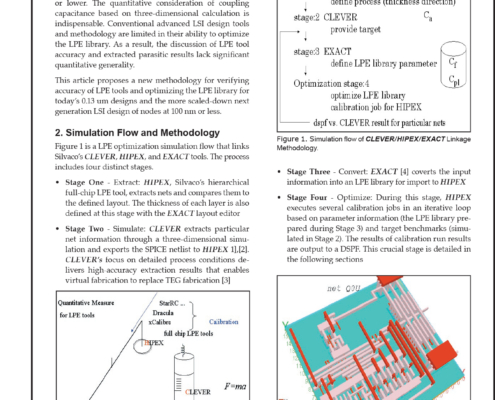

LPE Optimization with Clever/Hipex/Exact Linkage Methodology

On the cutting edge of LSI design, the accuracy of Layout Parasitic Extraction (LPE) tools is a critical issue to miniaturized LSI design of rules measuring 0.13 um or lower. The quantitative consideration of coupling capacitance based on three-dimensional calculation is indispensable. Conventional advanced LSI design tools and methodology are limited in their ability to optimize the LPE library. As a result, the discussion of LPE tool accuracy and extracted parasitic results lack significant quantitative generality.

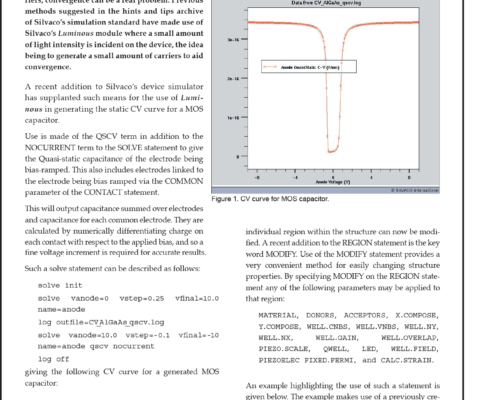

When solving for the static CV curve for a MOS capacitor, due to the absence of current carriers

When solving for the static CV curve for a MOS capacitor, due to the absence of current carriers, convergence can be a real problem. Previous methods suggested in the hints and tips archive of Silvaco’s simulation standard have made use of Silvaco’s Luminous module where a small amount of light intensity is incident on the device, the idea being to generate a small amount of carriers to aid convergence.

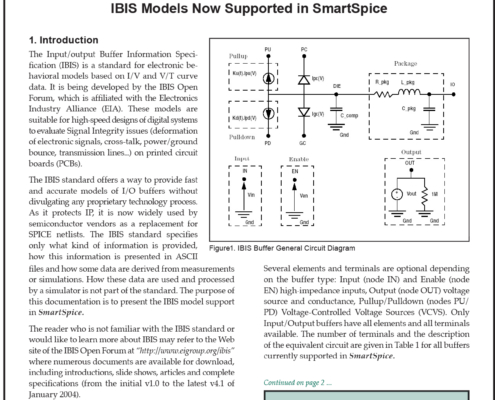

IBIS Models Now Supported in SmartSpice

Expert Parametric Wire (Pwire) is a complex group of objects containing, a single wire named master wire, any number of subparts such as enclosure wires, offset wires and sets of rectangles. Pwire objects enable extremely quick and efficient creation and editing of guard rings and shielded paths which are increasingly important due to higher integration density of IC designs.

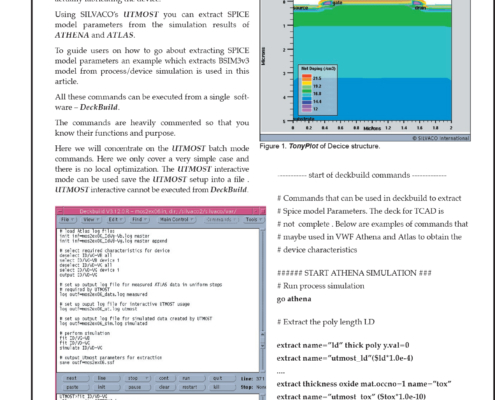

Extraction of SPICE Model Parameters from Atlas Device Simulation Using Utmost

Many users would like to extract SPICE models from their process and device simulation using Athena and Atlas to be used in actual circuit simulation without actually fabricating the device.

Using SILVACO's Utmost you can extract SPICE model parameters from the simulation results of Athena and Atlas.

Array Copying – Alignment from Specified Instance Number

For LCD and Memory designs, Array Copy function on Gateway is conveniently used. Users may want to align instances from specified instance number, for example starting from X100 or X1000. Here introduces a convenience way to realize it.

Hierarchical Layout versus Schematic

A new Hierarchical Layout versus Schematic (HLVS) system that provides significant improvement in verification of huge circuits is described. Other of LVS verification tools perform a netlist flattening and comparison in transistor level [1, 2]. These tools are based on standard graph isomorphism algorithms and are sufficiently efficient in practice.

Design of Optimal Spiral Inductors in Expert

Introduction

One of the key components in many RF ICs applications is the inductor. It is very important that the inductor has optimal design, meaning optimal geometry with the best possible characteristics [1]. Our computer-aided optimization technique using geometric programming (GP) has been used to find the optimum design for spiral inductors with different layout [2-4]. The goal is selection of the best geometry of inductors to find optimal values of inductor parameters (the number of turns and layout dimensions) and then drawing layouts of optimal inductors. Silvaco Expert is a powerful tool for drawing spiral inductors with different mask geometry (square, octagonal or circular). In this paper we presents a simple way to draw layouts of optimal inductors in Expert, without using parameterized cells.

When I do an extract, the generated layers are present in the layout.

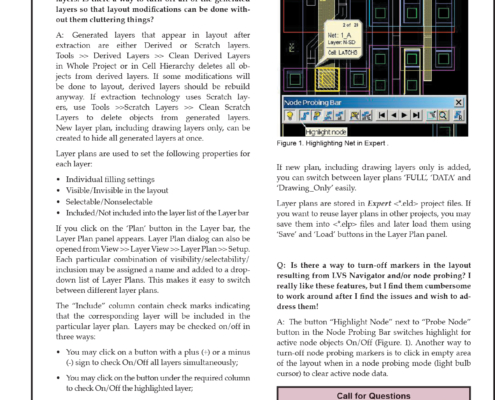

Q: When I do an extract, the generated layers are present in the layout. If I need to do layout modifications I find it very cumbersome to deal with the generated layers. Is there a way to turn-off all of the generated layers so that layout modifications can be done without them cluttering things?

Resistance Calculation Approach in Hipex-NET

Hipex-NET uses two techniques to calculate resistor values. First method of resistance extraction, which is usual for full chip netlist extractors and uses heuristic algorithms to recognize common shapes for which were obtained empirical formulas depending on geometry of resistor body and resistor terminals. Unfortunately, this method doesn’t cover the wide range of resistors and can handle only rectangular resistors, L-bends, and T-shaped resistive fragments. It also can be used to calculate resistance of snake and dog-bone shapes. We should also note that comparing to Maverick, Hipex-NET recognizes some new shapes as routine shapes for which resistance value can be calculated by the well-known formulas [1].

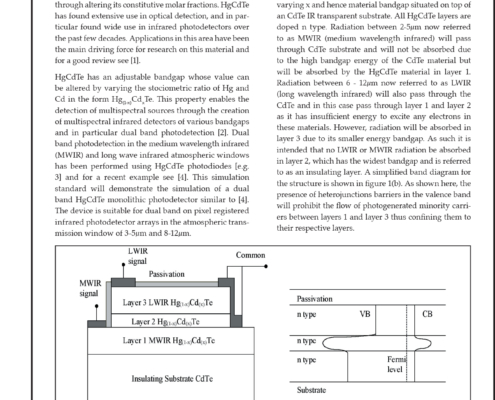

TCAD Simulation of a Dual Band Monolithic HgCdTe Infrared Photodetector

Introduction

Mercury cadmium telluride (HgCdTe) is a semiconductor material whose material properties are adjustable through altering its constitutive molar fractions. HgCdTe has found extensive use in optical detection, and in particular found wide use in infrared photodetectors over the past few decades. Applications in this area have been the main driving force for research on this material and for a good review see [1].