Simulating Selective and Non-Selective Epitaxy over Oxide Isolated Regions Using Athena

In certain cases, most notably in modern bipolar and SiGe HBT structures, epitaxial steps are performed after the oxide isolation structures have been already created. Thus the initial surface prior to epitaxy may contain regions of crystalline silicon, polysilicon or insulators, usually silicon dioxide. In the case of LOCOS isolation, the surface is also non-planar. In such epitaxial cases, epitaxy can be divided into two general types:-

Silvaco’s RFIC Design Suite

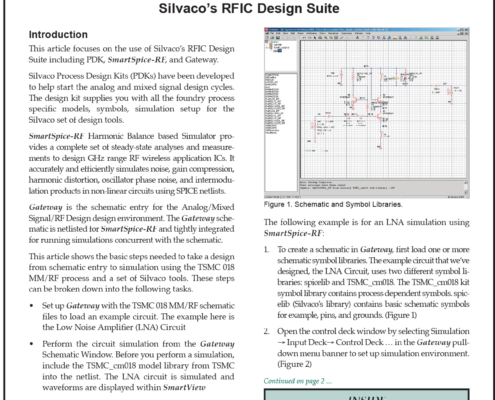

This article focuses on the use of Silvaco’s RFIC Design Suite including PDK, SmartSpice-RF, and Gateway.

HiSIM-1.2 Parameter Extraction with the Revised UTMOST-III Local Optimization Strategies

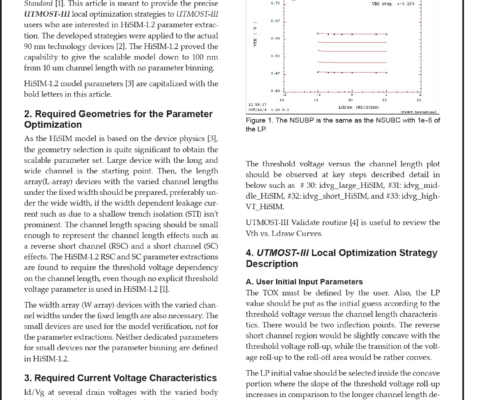

HiSIM-1.2 parameter extraction methodology was discussed in detail in a previous issue of Silvaco Simulation Standard [1]. This article is meant to provide the precise UTMOST-III local optimization strategies to UTMOST-III users who are interested in HiSIM-1.2 parameter extraction. The developed strategies were applied to the actual 90 nm technology devices [2]. The HiSIM-1.2 proved the capability to give the scalable model down to 100 nm from 10 um channel length with no parameter binning.

A Family Portrait of the BSIM Models

1. Introduction

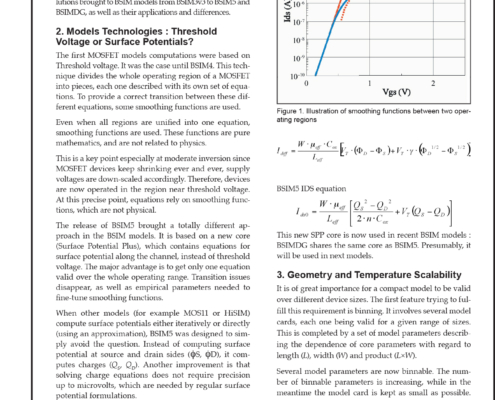

BSIM1, the first model of the BSIM series was released about ten years ago. Some major improvements have been made since that time, making the BSIM3v3 and BSIM4 models become worldwide standards. This article presents the evolutions brought to BSIM models from BSIM3v3 to BSIM5 and BSIMDG, as well as their applications and differences.

Customers are starting to use 64bit machines with large hard drives and Gigs of RAM

Customers are starting to use 64bit machines with large hard drives and Gigs of RAM and tend to forget the limitations imposed by a 32bit operating system. If you have more than 2Gigs of RAM in a system the extra is not used by the 32bit compiled program as it is not possible to address a contigeous memory space bigger than this when you have 1 parity bit and 31 data bits (2^31). If you are however using our 64bit compiled version of SmartSpice then you can use as much memory (RAM) as you care to put into the system (2^63 is a huge number compared to the 32 bit case).

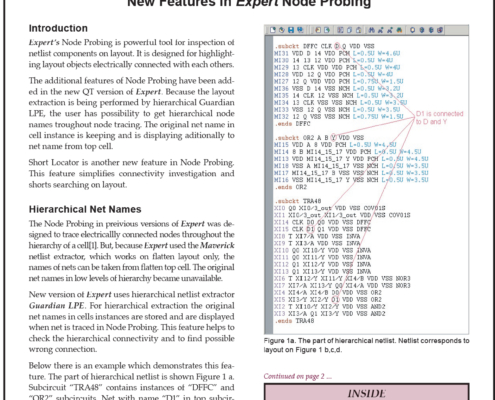

New Features in Expert Node Probing

Expert’s Node Probing is powerful tool for inspection of netlist components on layout. It is designed for highlighting layout objects electrically connected with each others.

The additional features of Node Probing have been added in the new QT version of Expert. Because the layout extraction is being performed by hierarchical Guardian LPE, the user has possibility to get hierarchical node names troughout node tracing. The original net name in cell instance is keeping and is displaying aditionally to net name from top cell.

Parasitic Capacitance Extraction with Hipex and Exact

Overview

To extract parasitic capacitances from a circuit layout, you need to perform the following steps:

Expert Layout Editor – New Commands Focus On Easier Operation

Expert layout editor version 4.0.1R has several new commands and functions released together with the new Qt GUI interface. Most of them are developed in order to improve easier operation.

Every time I create a new project or library, an empty cell with the same name is created in my project

Q. Every time I create a new project or library, an empty cell with the same name is created in my project. What do I need to setup to avoid the creation of this empty cell?

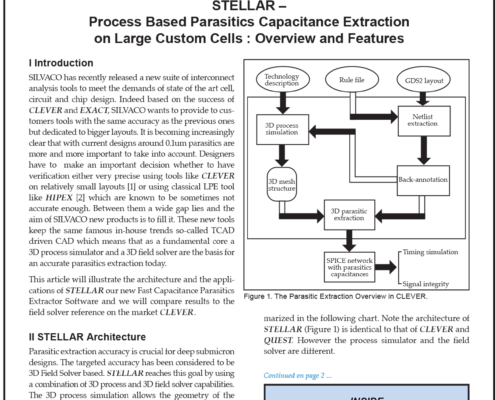

STELLAR – Process Based Parasitics Capacitance Extraction on Large Custom Cells

SILVACO has recently released a new suite of interconnect analysis tools to meet the demands of state of the art cell, circuit and chip design.