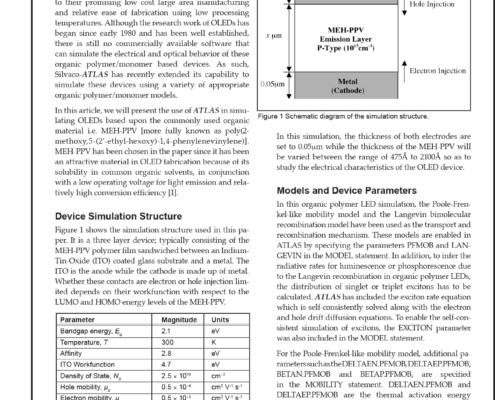

Simulating the Device Characteristics of MEH-PPV Polymer Light Emitting Diodes Using Atlas

Organic light emitting diodes (OLEDs) are attracting great interest in the display technology industry due to their promising low cost large area manufacturing and relative ease of fabrication using low processing temperatures. Although the research work of OLEDs has began since early 1980 and has been well established, there is still no commercially available software that can simulate the electrical and optical behavior of these organic polymer/monomer based devices. As such, Silvaco-ATLAS has recently extended its capability to simulate these devices using a variety of appropriate organic polymer/monomer models.

A Comprehensive Solution for Simulating Ultra-Shallow Junctions: From High Dose/Low Energy Implant to Diffusion Annealing

The persistent semiconductor technology trend of shrinking down device size requires development of veryaggressive technological setups consisting in high dose/low energy implants, followed by rapid thermal anneals (RTA).

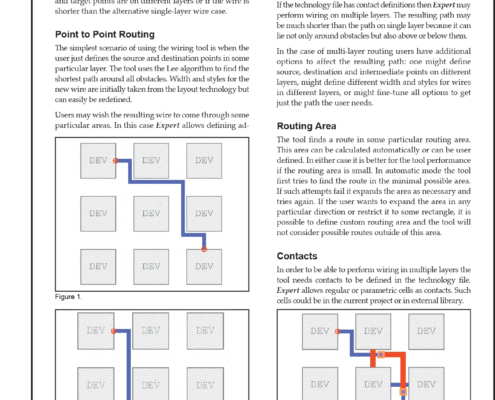

Expert: Wiring

The wiring tool in Expert automatically creates the shortest wire connecting two points specified by the user. The created wire goes around any existing layout objects. It may lie in multiple layers (multi-wire) if the source and target points are on different layers or if the wire is shorter than the alternative single-layer wire case.

I have to send copies of my project layout to different members of my group

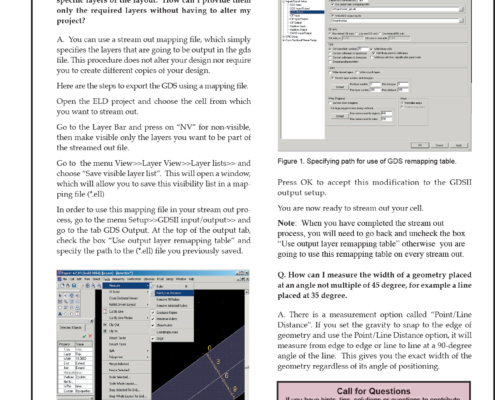

Q. I have to send copies of my project layout to different members of my group, but they need to see only specific layers of the layout. How can I provide them only the required layers without having to alter my project?

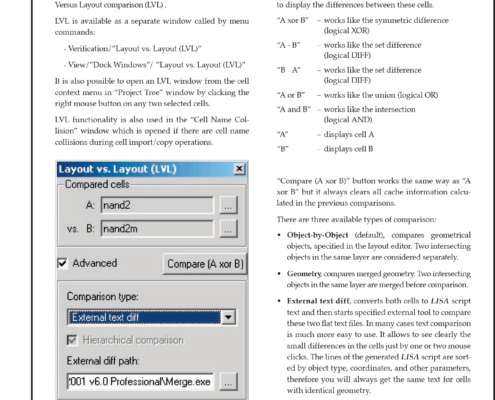

Expert: Layout Versus Layout (LVL) Comparison

Introduction

The functionality Silvaco’s Layou Editor, Expert, has recently been expanded with the new feature called Layout Versus Layout comparison (LVL).

LVL is available as a separate window called by menu commands:

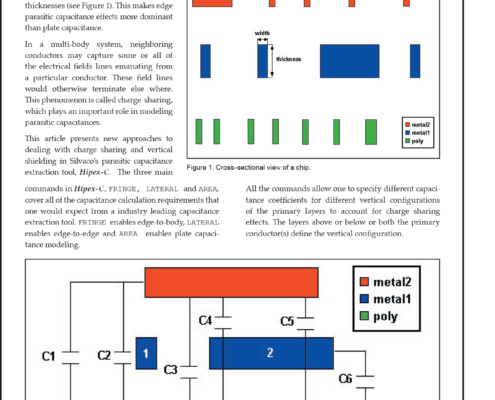

New Parasitic Capacitance Modeling in Hipex-C

In deep submicron technology, conduction layers have widths much smaller than their thicknesses (see Figure 1). This makes edge parasitic capacitance effects more dominant than plate capacitance.

In a multi-body system, neighboring conductors may capture some or all of the electrical fields lines emanating from a particular conductor. These field lines would otherwise terminate else where. This phenomenon is called charge sharing, which plays an important role in modeling parasitic capacitances.

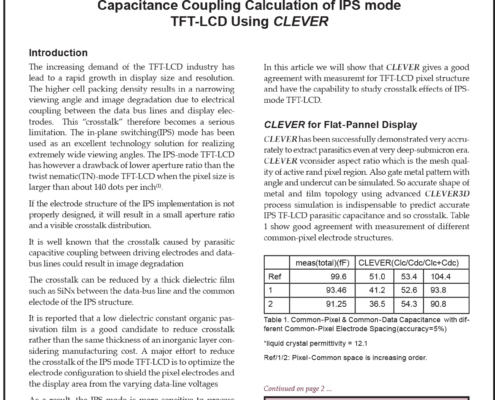

Capacitance Coupling Calculation of IPS mode TFT-LCD Using Clever

The increasing demand of the TFT-LCD industry has lead to a rapid growth in display size and resolution. The higher cell packing density results in a narrowing viewing angle and image degradation due to electrical coupling between the data bus lines and display electrodes. This “crosstalk” therefore becomes a serious limitation. The in-plane switching(IPS) mode has been used as an excellent technology solution for realizing extremely wide viewing angles.

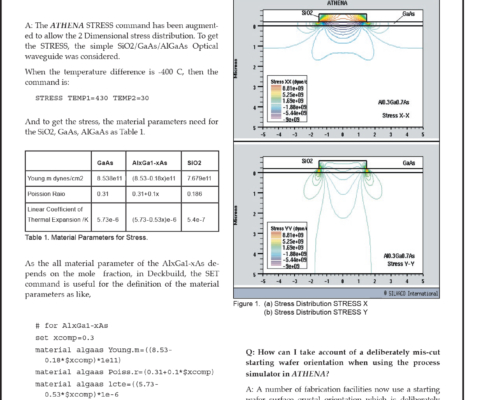

Can Athena get the STRESS in Compound Advanced material?

Q: Can ATHENA get the STRESS in Compound Advanced material?

A: The ATHENA STRESS command has been augmented to allow the 2 Dimensional stress distribution. To get the STRESS, the simple SiO2/GaAs/AlGaAs Optical waveguide was considered.

Simulating Selective and Non-Selective Epitaxy Over Oxide Isolated Regions Using Athena

In certain cases, most notably in modern bipolar and SiGe HBT structures, epitaxial steps are performed after the oxide isolation structures have been already created. Thus the initial surface prior to epitaxy may contain regions of crystalline silicon, polysilicon or insulators, usually silicon dioxide. In the case of LOCOS isolation, the surface is also non-planar.

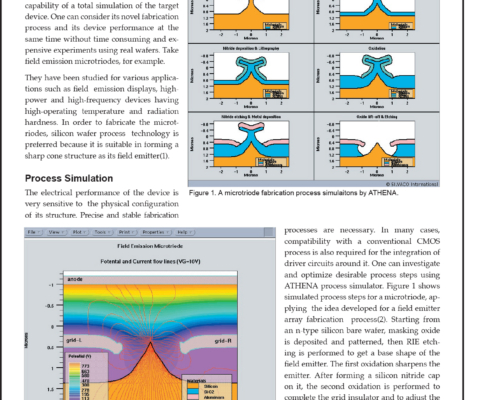

Process and Device Simulation of Field Emission Microtrides

One of the most beneficial merits of computer-based experiment using TCAD lies in its capability of a total simulation of the target device. One can consider its novel fabrication process and its device performance at the same time without time consuming and expensive experiments using real wafers. Take field emission microtriodes, for example.