TCAD Modeling and Data of NOR Nanocrystal Memories

Introduction

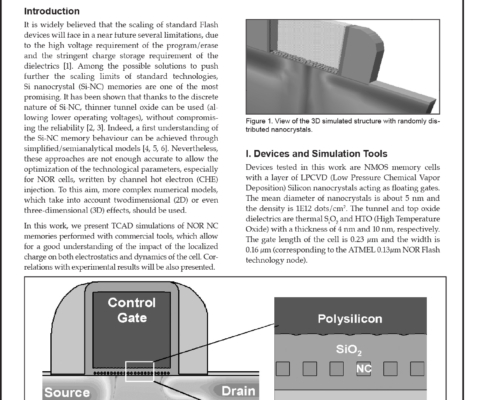

It is widely believed that the scaling of standard Flash devices will face in a near future several limitations, due to the high voltage requirement of the program/erase and the stringent charge storage requirement of the dielectrics [1]. Among the possible solutions to push further the scaling limits of standard technologies, Si nanocrystal (Si-NC) memories are one of the most promising. It has been shown that thanks to the discrete nature of Si-NC, thinner tunnel oxide can be used (allowing lower operating voltages), without compromising the reliability [2, 3]. Indeed, a first understanding of the Si-NC memory behaviour can be achieved through simplified/semianalytical models [4, 5, 6]. Nevertheless, these approaches are not enough accurate to allow the optimization of the technological parameters, especially for NOR cells, written by channel hot electron (CHE) injection. To this aim, more complex numerical models, which take into account twodimensional (2D) or even three-dimensional (3D) effects, should be used.

A Semi-Analytical Model for the Subthreshold Behavior of FinFLASH Structures

Abstract

In this paper we present an original semi-analytical model for the subthreshold electrical behavior of complex 3D structures as the SOI FinFLASH devices. This physically-based model, which does not need any fitting parameter, solves the Poisson equation for a fin covered by trapped charges in the active dielectrics. The analytical results are compared with fully 3D numerical simulations and a good agreement is obtained down to fins with very small feature sizes (order of tens of nm). This model can be efficiently used to gain information on important cell electrical behaviors as the threshold voltage shift Vth and the subthreshold slope factor S.

Is it possible to calculate the resistance components of a MOSFET

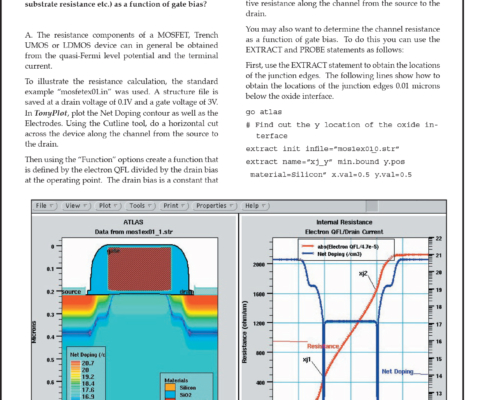

Q. Is it possible to calculate the resistance components of a MOSFET (i.e. channel resistance, epi resistance, substrate resistance etc.) as a function of gate bias?

Design Rules and Trends for Dummy Metal Filling Using Exact, Clever and Stellar

Introduction

The physical verification is becoming the most complex phase raised by the Deep SubMicron (DSM) technology. More than 50% of the design time is dedicated to the verification. With the shrink of transistors size, the interconnect delay is dominant versus gate delay. Hence the challenge in the DSM technology depends primarily on how to provide accurate characterization of these interconnects. This is especially the case when dummy metals are present.

Advanced Quantum Effects Simulation in Atlas

Introduction

The trend toward smaller MOSFET devices with thinner gate oxide and greater doping is resulting in the increased importance of quantum mechanical effects, which are observed as shifts in threshold voltage and gate capacitance. Predicting these quantum effects requires solving the Schrodinger equation. This article presents the Poisson-Schrodinger solver and recent enhancements implemented in ATLAS from Silvaco.

TCAD Simulation of a SONOS Device with Silvaco’s new FNONOS Model

Introduction

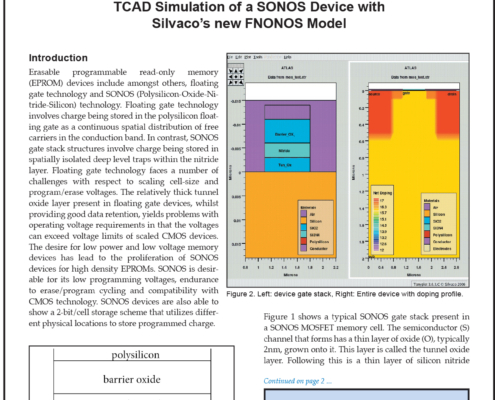

Erasable programmable read-only memory (EPROM) devices include amongst others, floating gate technology and SONOS (Polysilicon-Oxide-Nitride-Silicon) technology. Floating gate technology involves charge being stored in the polysilicon floating gate as a continuous spatial distribution of free carriers in the conduction band. In contrast, SONOS gate stack structures involve charge being stored in spatially isolated deep level traps within the nitride layer.

How to obtain a stable grid and smooth doping profile in non-planar a-Si TFT using Athena/Elite?

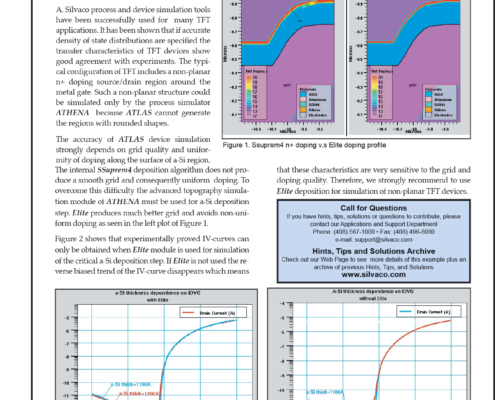

How to obtain a stable grid and smooth doping profile in non-planar a-Si TFT using Athena/Elite?

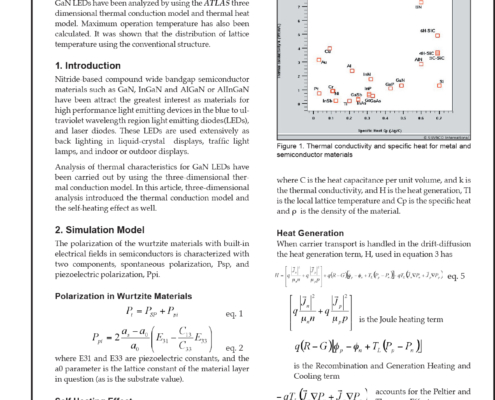

Three Dimensional Electro-Thermodynamic Analysis for GaN Light Emitting Diodes

Abstract

Improvement in temperature characteristics of GaN LEDs is important for realizing reliable devices operating at high temperatures. In this article, the thermal characteristics of GaN LEDs have been analyzed by using the ATLAS three dimensional thermal conduction model and thermal heat model. Maximum operation temperature has also been calculated. It was shown that the distribution of lattice temperature using the conventional structure.

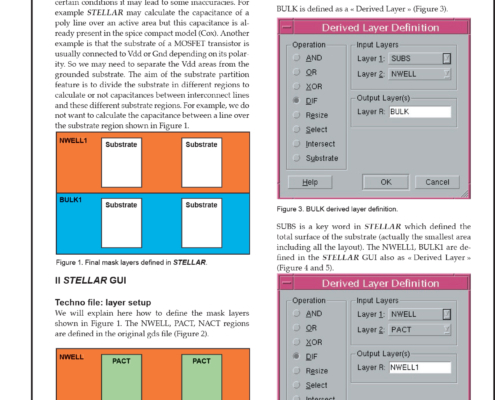

Accurate Spice Netlist Extraction in Stellar Using New Substrate Partition Feature

Introduction

By default STELLAR calculates the capacitances between interconnect lines and the whole substrate. In certain conditions it may lead to some inaccuracies. For example STELLAR may calculate the capacitance of a poly line over an active area but this capacitance is already present in the spice compact model (Cox). Another example is that the substrate of a MOSFET transistor is usually connected to Vdd or Gnd depending on its polarity.

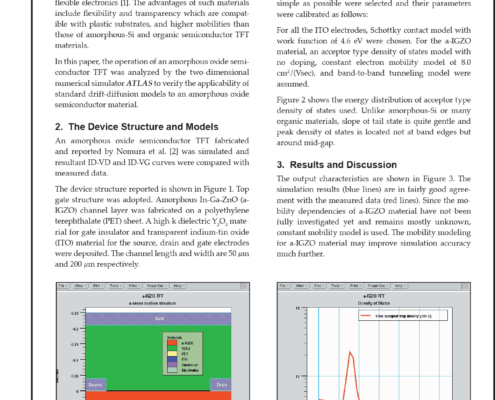

Atlas Device Simulation of Amorphous Oxide Semiconductor Thin-Film Transistors

1. Introduction

Amorphous oxide semiconductor materials have attracted much attention as key components of TFTs for flexible electronics [1]. The advantages of such materials include flexibility and transparency which are compatible with plastic substrates, and higher mobilities than those of amorphous-Si and organic semiconductor TFT materials.