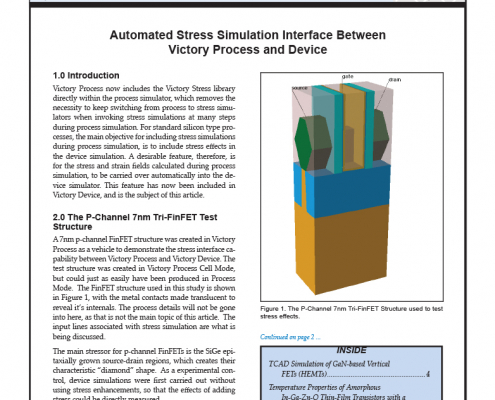

Automated Stress Simulation Interface Between Victory Process and Device

Victory Process now includes the Victory Stress library directly within the process simulator, which removes the necessity to keep switching from process to stress simulators when invoking stress simulations at many steps during process simulation. For standard silicon type processes, the main objective for including stress simulations during process simulation, is to include stress effects in the device simulation. A desirable feature, therefore, is for the stress and strain fields calculated during process simulation, to be carried over automatically into the device simulator. This feature has now been included in Victory Device, and is the subject of this article.

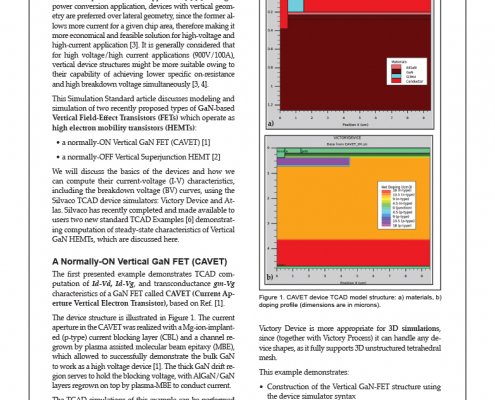

TCAD Simulation of GaN-based Vertical FETs (HEMTs)

Gallium nitride (GaN)-based devices have entered the power electronics market and are showing excellent progress in the medium power conversion application [1]-[5]. For high-power conversion application, devices with vertical geometry are preferred over lateral geometry, since the former allows more current for a given chip area, therefore making it more economical and feasible solution for high-voltage and high-current application [3]. It is generally considered that for high voltage/high current applications (900V/100A), vertical device structures might be more suitable owing to their capability of achieving lower specific on-resistance and high breakdown voltage simultaneously [3, 4].

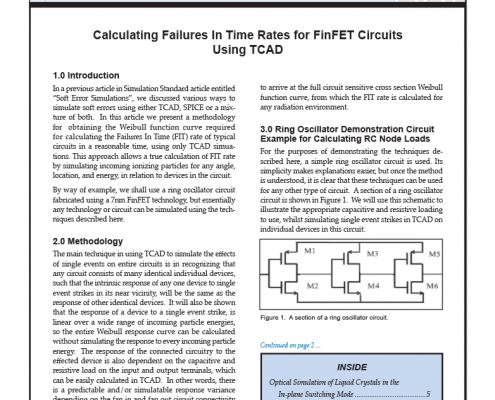

Calculating Failures In Time Rates for FinFET Circuits Using TCAD

In a previous article in Simulation Standard article entitled “Soft Error Simulations”, we discussed various ways to simulate soft errors using either TCAD, SPICE or a mixture of both. In this article we present a methodology for obtaining the Weibull function curve required for calculating the Failures In Time (FIT) rate of typical circuits in a reasonable time, using only TCAD simuations. This approach allows a true calculation of FIT rate by simulating incoming ionizing particles for any angle, location, and energy, in relation to devices in the circuit.

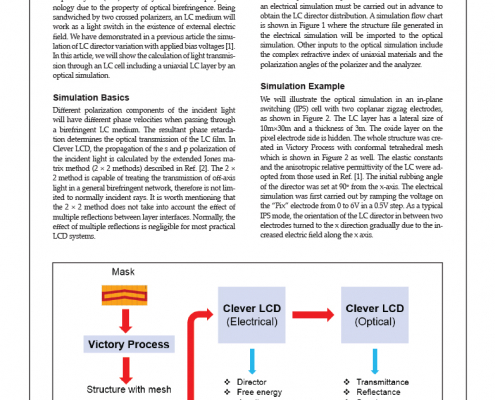

Optical Simulation of Liquid Crystals in the In-plane Switching Mode

Liquid Crystals (LCs) are widely used in the display technology due to the property of optical birefringence. Being sandwiched by two crossed polarizers, an LC medium will work as a light switch in the existence of external electric field. We have demonstrated in a previous article the simulation of LC director variation with applied bias voltages [1]. In this article, we will show the calculation of light transmission through an LC cell including a uniaxial LC layer by an optical simulation.

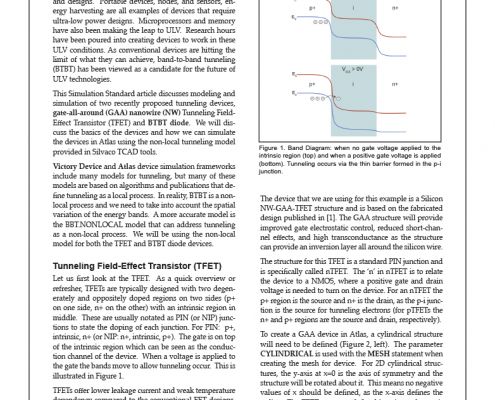

TCAD Simulations of TFET and Tunneling Diode

Researchers and designers are looking into a future of ultra-low power and ultra-low voltage (ULV) devices and designs. Portable devices, nodes, and sensors, energy harvesting are all examples of devices that require ultra-low power designs. Microprocessors and memory have also been making the leap to ULV. Research hours have been poured into creating devices to work in these ULV conditions. As conventional devices are hitting the limit of what they can achieve, band-to-band tunneling (BTBT) has been viewed as a candidate for the future of ULV technologies.

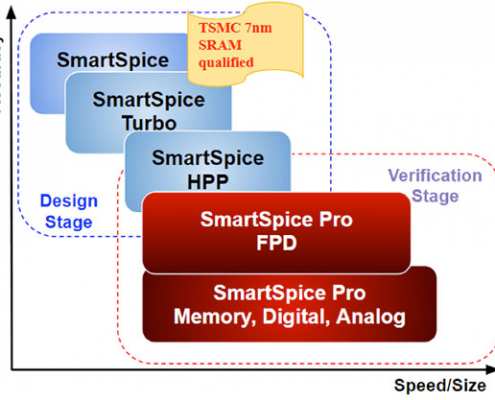

TFT Panel Simulation Using SmartSpice Pro

TFT panels have already gained their undisputable reputation in a variety of professional and commercial applications. High quality, ease of customization, and comparably low manufacturing costs position these panels as an attractive solution offered by standard and custom color display industry. To accomplish the goals set by ever increasing quality standards, TFT panel circuits constantly expand their functionality, add new features. This process naturally leads to an increased complexity of the display systems and, as a consequence, is accompanied by a strong demand for higher operating speeds. Traditionally, implementation of the solutions satisfying these tough requirements in the industry is accompanied by device feature size reduction and by placing more and more elements of the system chips. Modern TFT panel circuits contain millions of active and passive devices and their chip sizes continue to grow with every new generation.

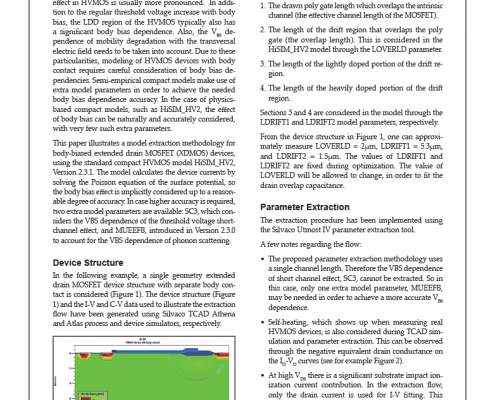

Model Extraction for Body-Biased XDMOS Devices

Compared with regular MOSFET devices, the body bias effect in HVMOS is usually more pronounced. In addition to the regular threshold voltage increase with body bias, the LDD region of the HVMOS typically also has a significant body bias dependence. Also, the VBS dependence of mobility degradation with the transversal electric field needs to be taken into account. Due to these particularities, modeling of HVMOS devices with body contact requires careful consideration of body bias dependencies. Semi-empirical compact models make use of extra model parameters in order to achieve the needed body bias dependence accuracy. In the case of physics-based compact models, such as HiSIM_HV2, the effect of body bias can be naturally and accurately considered, with very few such extra parameters.

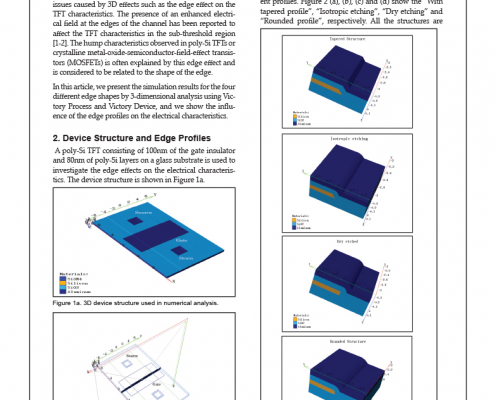

Edge Effect Analysis on TFT Devices Using 3D Numerical Simulation

3D TFT analysis has been getting lots of attention due to issues caused by 3D effects such as the edge effect on the TFT characteristics. The presence of an enhanced electrical field at the edges of the channel has been reported to affect the TFT characteristics in the sub-threshold region [1-2]. The hump characteristics observed in poly-Si TFTs or crystalline metal-oxide-semiconductor-field-effect transistors (MOSFETs) is often explained by this edge effect and is considered to be related to the shape of the edge.

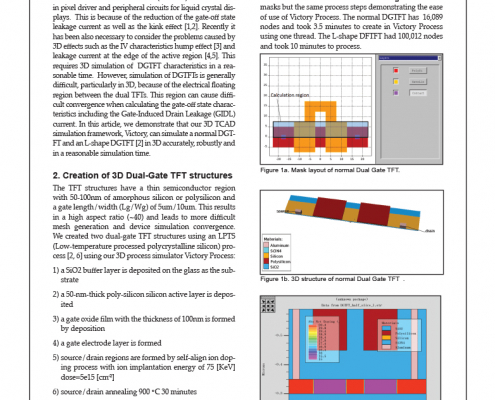

3D Simulation of Dual-Gate Thin Film Transistors

Dual-Gate Thin Film Transistors (DGTFTs) are often used in pixel driver and peripheral circuits for liquid crystal displays. This is because of the reduction of the gate-off state leakage current as well as the kink effect [1,2]. Recently it has been also necessary to consider the problems caused by 3D effects such as the IV characteristics hump effect [3] and leakage current at the edge of the active region [4,5]. This requires 3D simulation of DGTFT characteristics in a reasonable time. However, simulation of DGTFTs is generally difficult, particularly in 3D, because of the electrical floating region between the dual TFTs. This region can cause difficult convergence when calculating the gate-off state characteristics including the Gate-Induced Drain Leakage (GIDL) current. In this article, we demonstrate that our 3D TCAD simulation framework, Victory, can simulate a normal DGTFT and an L-shape DGTFT [2] in 3D accurately, robustly and in a reasonable simulation time.

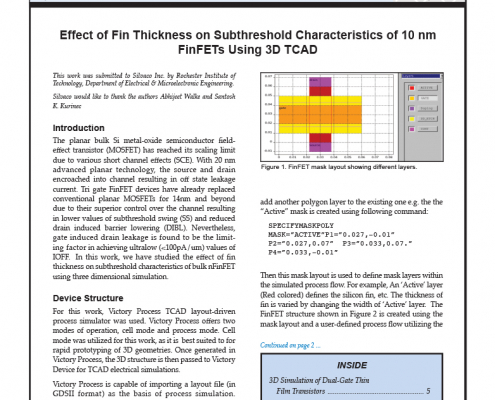

Effect of Fin Thickness on Subthreshold Characteristics of 10 nm FinFETs Using 3D TCAD

The planar bulk Si metal-oxide semiconductor field-effect transistor (MOSFET) has reached its scaling limit due to various short channel effects (SCE). With 20 nm advanced planar technology, the source and drain encroached into channel resulting in off state leakage current. Tri gate FinFET devices have already replaced conventional planar MOSFETs for 14nm and beyond due to their superior control over the channel resulting in lower values of subthreshold swing (SS) and reduced drain induced barrier lowering (DIBL). Nevertheless, gate induced drain leakage is found to be the limiting factor in achieving ultralow (<100pA/um) values of IOFF. In this work, we have studied the effect of fin thickness on subthreshold characteristics of bulk nFinFET using three dimensional simulation.