Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

How do I create complex shapes with fixed cross sections in Victory Mesh?

Victory Mesh versions 1.7.2.C and later include two new commands that can be used for complex shape genera-tion. The path and follow commands can be used together to generate surface meshes of general shapes based on fixed cross sections.

PathThe path command connects a sequence of vertices via edges. The command operates in line or Bezier modes. In the line mode the from/to parameters are used to define the start and end of an n-dimensional line segment, for example:

Parabolic Grading of a PHEMT Channel Composition for Ultra-High and Broad OIP3 Peak

We detect a local maximum in the design space of a pseudomorphic-channel high electron mobility transistor (PHEMT). The design has an OIP3 linearity figure-of-merit that is 10-15 dBm above the baseline for a similar 1 mm width control device, and is achieved at a gate bias on the order of 100 mA/mm or less, where the ratio of transconductance to the bias current gm1/ID is particularly large (7 volt-1).

TCAD Investigation of Total Ionizing Dose (TID) Effects on Gallium Nitride HEMTs

Gallium Nitride (GaN) based devices such as the High Electron Mobility Transistors (HEMTs) find wide applications in RF and Power domain due to its excellent intrinsic properties. Accordingly, such devices have also been explored for their radiation hardness which is inherent due to the strong bonding nature of the binary and ternary nitrides. Radiation-induced instabilities including the radiation-induced stress and changes to the material properties leading to the departure of expected results in practical applications. Due to the limited availability of the test structures and facilities required to analyze the reliability of said devices under ionizing radiations, the cost and time of production gets affected. In this regard, to cut down on the cost and time for production, device engineers require accurate and reliable tools that can accurately predict the robustness of their proposed device architectures in foreign environments. Silvaco’s Victory TCAD software is one such tool that can aid the device engineers in this aspect. In this work, we demonstrate the Total Ionizing Dose (TID) Effects on GaN HEMTs using the Radiation Effects Module (REM) available with Silvaco’s Victory TCAD suite.

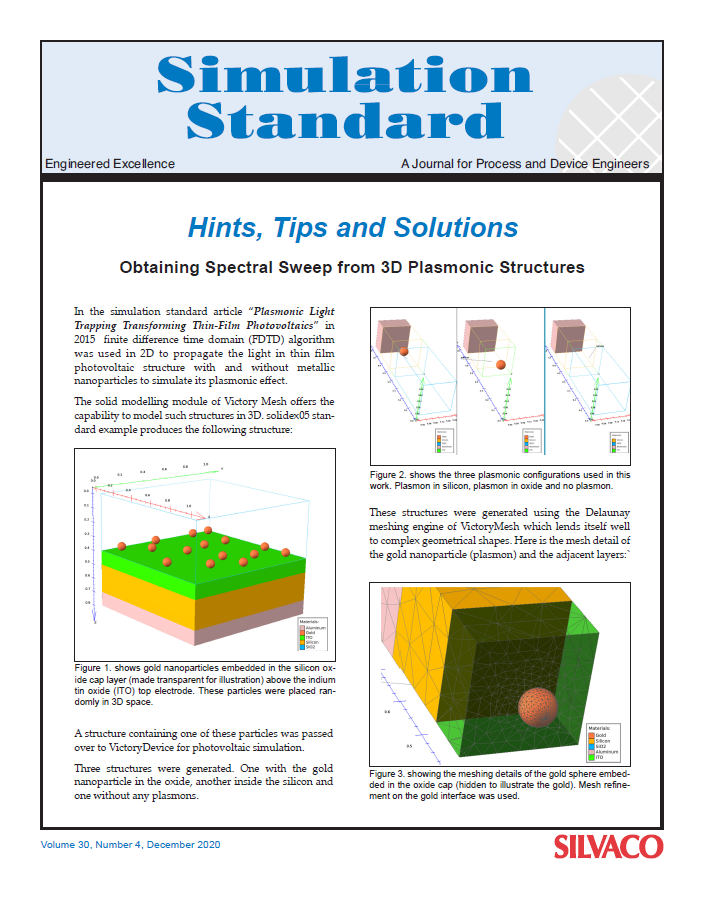

Obtaining Spectral Sweeps from 3D Plasmonic Structures

In the simulation standard article, “Plasmonic Light Trapping Transforming Thin-Film Photovoltaics” from 2015, the finite difference time domain (FDTD) algorithm was used in 2D to propagate the light in thin film photovoltaic structures with and without metallic nanoparticles to simulate its plasmonic effect. The solid modeling module of Victory Mesh offers the capability to model such structures in 3D.

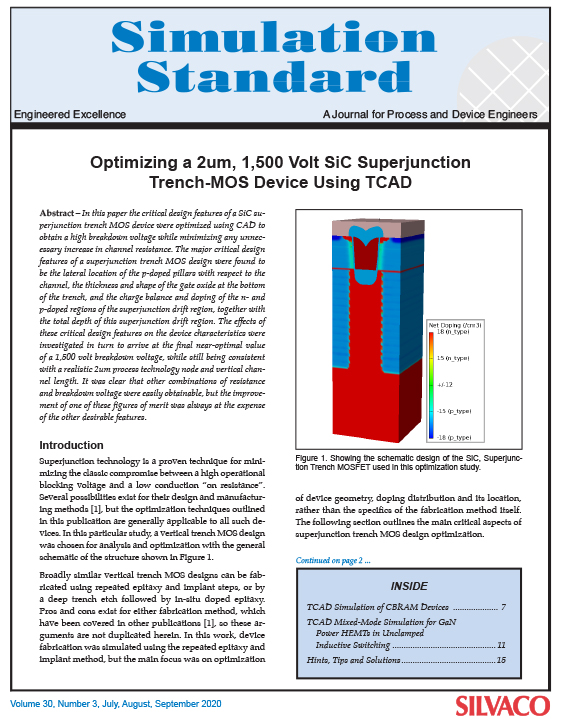

Optimizing a 2um, 1,500 Volt SiC Superjunction Trench-MOS Device Using TCAD

In this paper the critical design features of a SiC superjunction trench MOS device were optimized using CAD to obtain a high breakdown voltage while minimizing any unnecessary increase in channel resistance.

TCAD Simulation of CBRAM Devices

Conductive Bridge Random Access Memory (CBRAM) is a non-volatile memory device technology that can operate by consuming very low power. Another advantage of the CBRAM devices is its ability to be easily integrated into conventional back-end-of-line CMOS processes [1].