SmartSpice Circuit Simulator

실바코의 SmartSpice™는 업계 최고의 정밀도를 제공하는 고성능 병렬 SPICE 시뮬레이터입니다. 이 제품은 복잡한 고정밀 아날로그, 믹스드 시그널 회로 시뮬레이션, 메모리, 맞춤형 디지털 설계 및 첨단 반도체 공정의 셀 라이브러리 특성화 등에 적용할 수 있는 검증된 종합 솔루션입니다.

실바코의 SmartSpice는 다중 솔버, 스테핑 알고리즘 및 계산 기술을 구현하는 지능형 아키텍처를 사용합니다. 그 결과, 정확하고 강력한 컨버전스 및 업계 최고의 성능과 용량 (8백만개 이상의 능동 소자)을 실현할 수 있습니다. HSPICE® 및 Spectre®와 호환되며, 최신 기술 (TFT, OTFT, SOI, HBT, FRAM, FinFET 등)에 대해 보정된 SPICE 모델을 지원합니다. 실바코의 Gateway 스키매틱 편집기 및 SmartView 파형 뷰어와 통합되어, 프론트 엔드의 아날로그 IC 설계 플로우에 최적인 툴입니다. 신속한 분석을 위해 멀티 스레드 병렬 시뮬레이션 및 네트워크의 CPU를 이용한 분산 멀티 프로세싱을 지원합니다.

적용

- 아날로그, 믹스드 시그널

- 메모리 설계

- FPD 설계

- 커스텀 디지털

- 라이브러리 특성 추출

실시간 회로 시뮬레이션 러버밴드 기능

SmartSpice 및 Gateway의 러버밴드 기능으로, 아날로그 디자인의 개선이 용이합니다. 모델의 값이나 소자 인스턴스 파라미터를 변경하여, 러버밴드 기능을 통해 회로 성능의 변화를 실시간으로 확인할 수 있습니다.

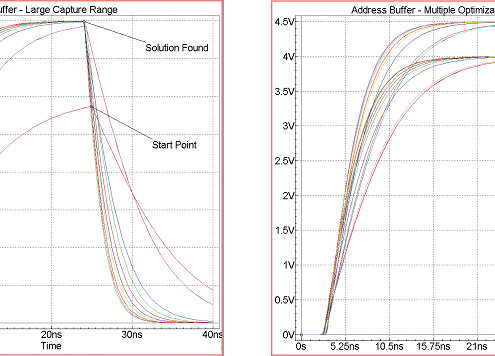

기본 최적화

SmartSpice는 회로의 파라미터 최적화를 수행합니다. 최적화 툴은 포괄적인 인터페이스와 대화형 디스플레이 시스템을 제공하여, 최적화 과정을 시각적으로 확인할 수 있습니다. 성능 측정 및 함수 커브의 최적화를 지원합니다.

성능 측정 최적화

- 각각의 전기적 특성이 사양에 맞도록 회로 구성요소의 값과 파라미터를 자동으로 변경

- Optimizer가 지연, 상승/하강 시간, 트립 포인트, 최대/최소 전류, 기타 회로의 성능 측정값을 세밀하게 조정하여, SmartSpice의 .MEASURE 구문으로 계산 가능

- 다양한 성능 측정을 위해 여러 목표를 동시에 최적화하는 것이 가능

함수 커브 최적화

- 함수 커브 최적화 기능으로 DC, AC, 과도 분석에 대해 계산된 커브를 원하는 커브에 부합. 원하는 커브는 TCAD 시뮬레이션의 결과 또는 물리적인 측정값을 표현 가능

- 수행할 회로 분석의 유형은 제한 없음. 정상 상태, 주파수, 시간 도메인에서 회로 최적화 가능

Verilog-A 언어 환경

SmartSpice를 위한 Verilog-A 모델링 확장 언어는 회로 설계자와 모델 개발자에게 복잡한 아날로그 회로 및 믹스드 시그널 회로와 모델 설계 및 검증을 위해 편리하고 포괄적인 환경을 제공합니다. 성능 모델링을 통해 아날로그 및 믹스드 시그널 디자인의 하향식 설계와 상향식 검증을 지원합니다. Verilog-A 소스 코드의 컴파일 및 암호화를 통해 소스의 공개 없이 독점 모델과 아날로그 IP를 배포할 수 있습니다.

주요 특징

- 디버거와 개발 환경을 통합하여 컴팩트 성능 모델을 신속하게 개발

- Verilog-AMS 2.3.1 언어 사양의 모든 아날로그 특징과 호환

- 다양한 분포 (가우시안, exponential, Poisson, chi-square, Student’s T, Erlang)에서 소신호와 노이즈 소스를 구현

- 시간 미적분, 편미분, transition, slew, Laplace transform, Z-transform을 포함하여, 아날로그 연산을 실행

- 아날로그 설계자는 세부적인 회로 설계 전에 프로토타입 목적으로 PLL, VCO, A/D, D/A 등의 설계를 위한 실행 파일 빌드 가능

- 설계자는 Sigma-Delta 컨버터처럼 믹스드-시그널 설계를 위한 서브서킷으로서 디지털 콤포넌트를 형성 가능

Viso를 활용한 기생 문제의 조사, 분석 및 해결

Si, GaN, SiC 기술에 대한 전력 소자 SPICE 모델링

SmartSpice를 활용하여 최신 TFT 기반 플랫 패널 설계

Utmost IV를 활용한 소자 모델링의 최신 기술

실바코 플로우를 활용한 FPD 및 검출기의 픽셀 어레이 설계 및 시뮬레이션