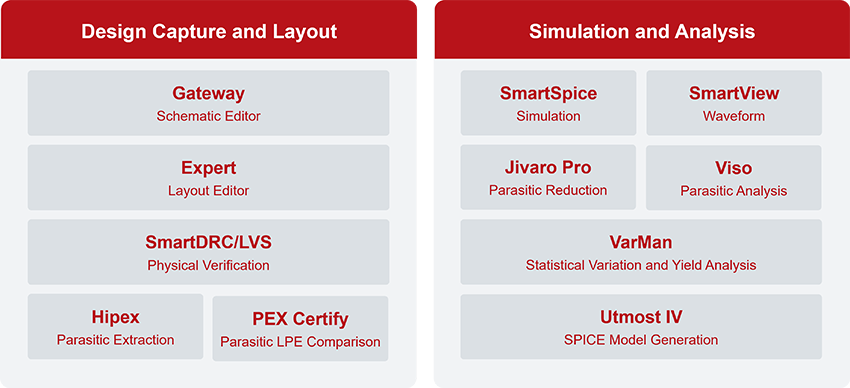

アナログIC-CAD設計フル・フロー

シルバコは、回路図作成、回路シミュレーション、レイアウト設計、物理検証、寄生素子抽出および寄生素子リダクション、そして統計的ばらつきや歩留まり解析を含むポスト・レイアウト解析をはじめとする完全なIC-CAD設計フローを提供します。

Schematic Editor

Layout Editor

Physical Verification

Parasitic Extraction

Circuit Simulation

Waveform Analyzer

Parasitic Reduction

Parasitic Analyzer and Debugger

Statistical Variation and Yield Analysis

Device Characterization and SPICE Modeling

Parasitic Extraction Comparison

スケマティック・エディタ

Gatewayは、直感的な編集機能、大規模、複雑な多階層またはフラットなデザインに対応する作業効率の高い回路図設計環境です。既存のネットリストからシンボルを自動生成する機能、業界標準の各種ネットリストおよびインタフェース・フォーマットをサポートしています。Gatewayは、シルバコのTCAD、およびアナログ・カスタム設計ツールと 緊密に統合されています。

レイアウト・エディタ

Expertは、アナログ、ミックスドシグナル、RF、およびデジタル回路において、幅広いシリコン・テクノロジにわたった大規模レイアウトが編集可能な、柔軟性を備えた階層型ICレイアウト・エディタです。Expertは、シルバコのカスタムIC設計スイートの重要な鍵として、Gatewayの回路図設計、および SmartDRC/LVS 物理検証環境とシームレスに統合されています。また、Calibre® RealTimeとのリンクにより、サインオフ品質のDRCをインタラクティブおよびオンデマンドで提供します。Expertの直感的なインタフェース、容易な設定作業、インタラクティブなルール・チェックにより、正確なレイアウトの迅速な作成を可能とし、素早いテープアウトを実現できます。

DRC/LVS物理検証

SmartDRC/LVS は、DRC (デザイン・ルール・チェック)、LVS (レイアウト対スケマティック) 比較、およびレイアウト・ネットリスト抽出を含む、アナログ、デジタル、およびミックスドシグナルICの物理検証を実行します。独自のアーキテクチャにより、マルチCPUによる高い性能とキャパシティ、複雑な形状の正確な処理、高速なインタラクティブ検証と直感的なデバッグによる優れた生産性を実現しています。

フルチップ寄生素子抽出

Hipexは、アナログ、ミックスドシグナル、メモリIC、SoCデザインの階層レイアウトから寄生容量と寄生抵抗の抽出を高精度かつ高速に実現するソリューションを提供します。Hipexは、シルバコの物理ICデザイン・フローを構成するツールの1つであり、Expertレイアウト・エディタと緊密に連携することで、DRC/LVS検証のみならず、寄生RC抽出の実行も可能とします。また、高速パターン・マッチングおよびフィールド・ソルバ・モードの両方に対応します。

回路シミュレーション

SmartSpiceは、アクティブ・デバイス・モデル一式、Verilog-Aコンパクト・モデル、スケマティック、レイアウト、およびTCAD解析ツールとの緊密な統合を提供する高パフォーマンスのパラレルSPICEシミュレータです。Smartspiceは、複雑で精密なアナログ/ミックスドシグナル回路、メモリ、およびカスタム・デジタル・デザインのシミュレーションを含む用途に使用でき、先進半導体プロセスのセル・ライブラリのキャラクタライズにも適した、実証済みの包括的なソリューションです。

寄生素子リダクション

Jivaro Proは、増大するポストレイアウト・シミュレーションの時間とリソースの管理という課題に対処するため、世界の主要なIDMおよびファブレス企業により採用されています。Jivaro Proは、寄生素子をリダクションする特許取得済みの数学的アプローチを適用し、精度を維持しながら回路の複雑性を低減します。

寄生素子解析

Visoは、設計の性能目標に影響を与える寄生効果を迅速かつ包括的に解析することができます。また、ロバストな解析を通じて、クロストーク効果、信号の弱点、アンバランスなネット対称性、遅延の劣化、IRドロップ問題など、さまざまな問題に対処することができます。

寄生素子抽出の比較

PEX Certify (PEX DiffとPEX Linkで構成) は、抽出された大規模なネットリストを比較して、相違点についての評価と定量化が行えるように設計されています。PEX Certifyは、長時間の回路シミュレーションを実行することなく統計と寄生素子の高度な解析を使用して、抽出された2つのネットリストが一致するかどうかを非常に迅速に判断することが可能です。

ばらつき解析

VarManは包括的な解析ツール・スイートで、設計者は統計的ばらつきを正確に把握し、実装の適切な決定を事前に行うことができます。VarManは、マシンラーニング・テクノロジを採用し、アナログ、RF、スタンダード・セル、IO、およびメモリ設計に向けた効率的で信頼性の高いソリューションを提供する新世代のツールです。

SPICEモデル生成

シルバコのUtmost IVは、アドバンスドCMOSや化合物半導体デバイスの特性解析に伴うさまざまな難しい課題に対応し、これらのモデリングを行うことができる、業界をリードするソリューションです。Utmost IVは、半導体デバイスの特性解析、高精度・高品質のSPICEモデル、マクロ・モデル、およびVerilog-Aモデルの生成のための使いやすいデータベース・ドリブン環境を提供します。アナログ、ミックスドシグナル、RFの各用途に利用できます。

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

新機能Design Explorerを使ったアナログ回路設計とポストレイアウト・シミュレーション

SmartSpice Signal Integrity 最新機能の紹介

RPI TFTモデルの理解と実装(2)リーク電流モデル