Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

New Features in SmartSpice 2.3.4.C

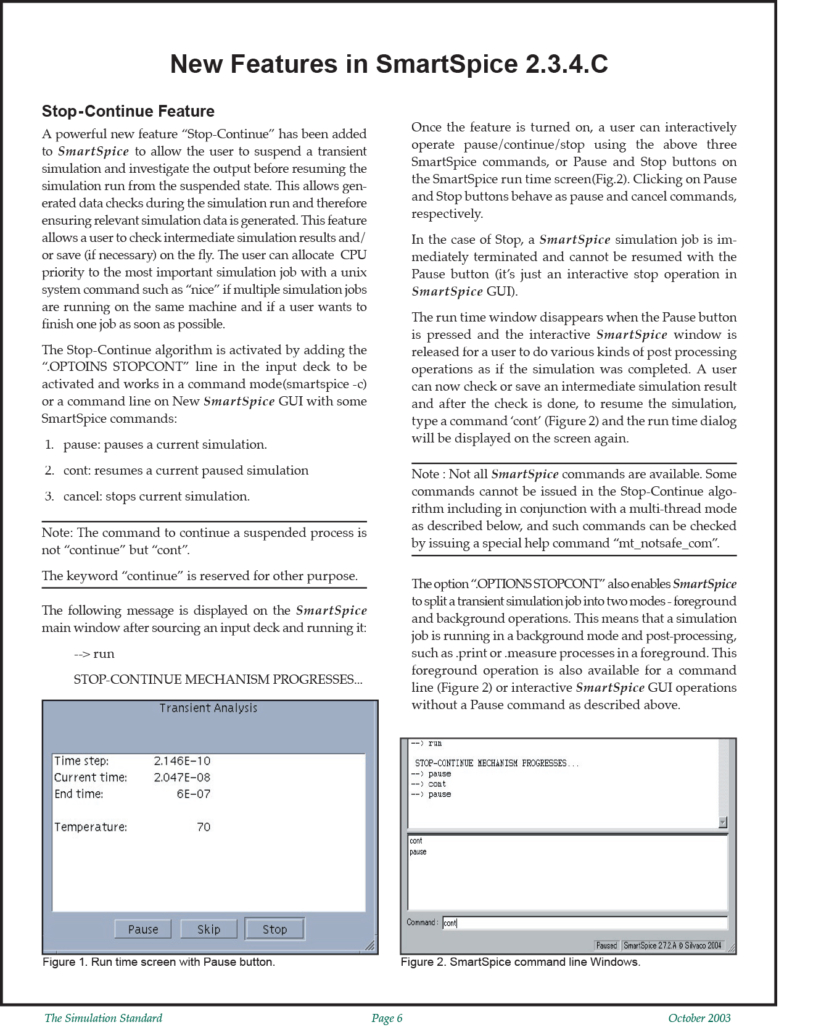

A powerful new feature “Stop-Continue” has been added to SmartSpice to allow the user to suspend a transient simulation and investigate the output before resuming the simulation run from the suspended state. This allows generated data checks during the simulation run and therefore ensuring relevant simulation data is generated. This feature allows a user to check intermediate simulation results and/or save (if necessary) on the fly.

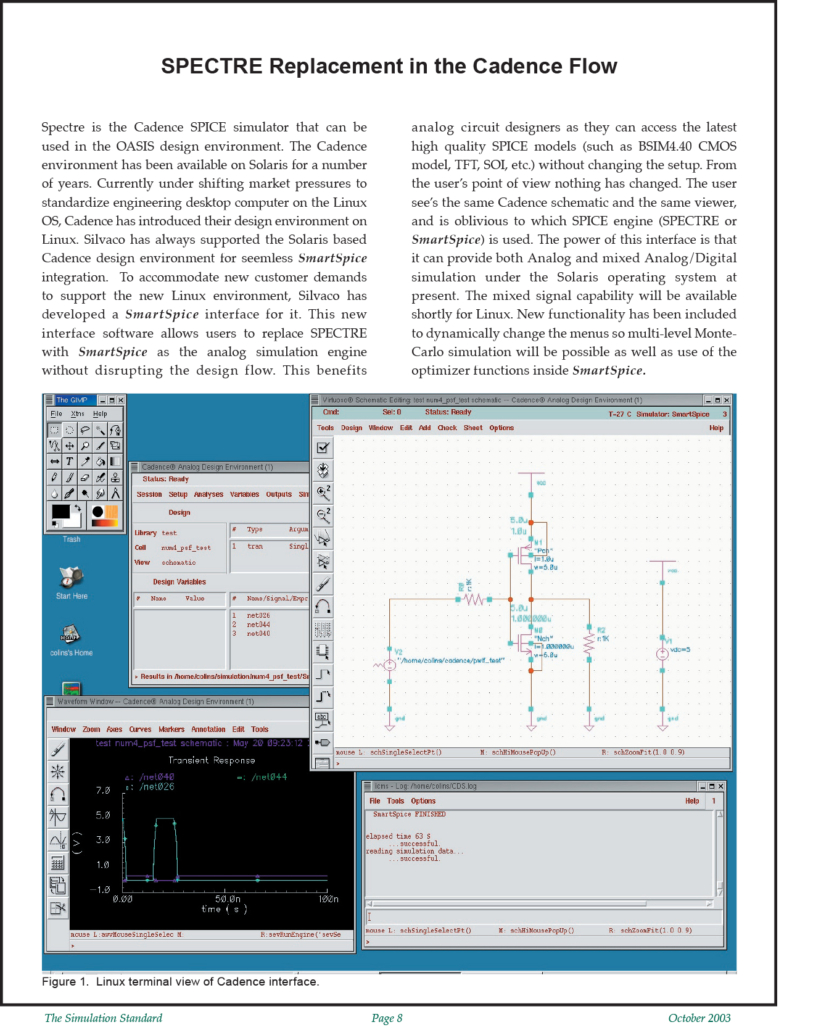

Spectre® Replacement in the Cadence Flow

Silvaco has always supported the Solaris based Cadence design environment for seemless SmartSpice integration. To accommodate new customer demands to support the new Linux environment, Silvaco has developed a SmartSpice interface for it. This new interface software allows users to replace Spectre with SmartSpice as the analog simulation engine without disrupting the design flow.

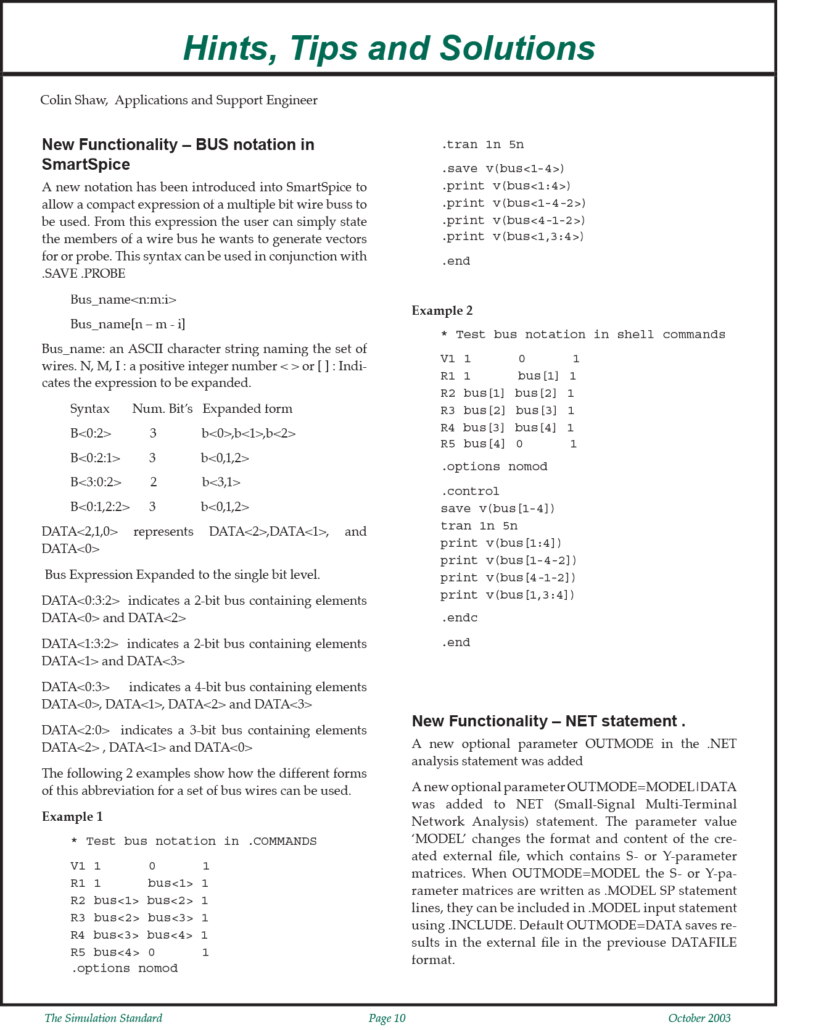

New Functionality – BUS notation in SmartSpice

A new notation has been introduced into SmartSpice to allow a compact expression of a multiple bit wire buss to be used. From this expression the user can simply state the members of a wire bus he wants to generate vectors for or probe. This syntax can be used in conjunction with .SAVE .PROBE

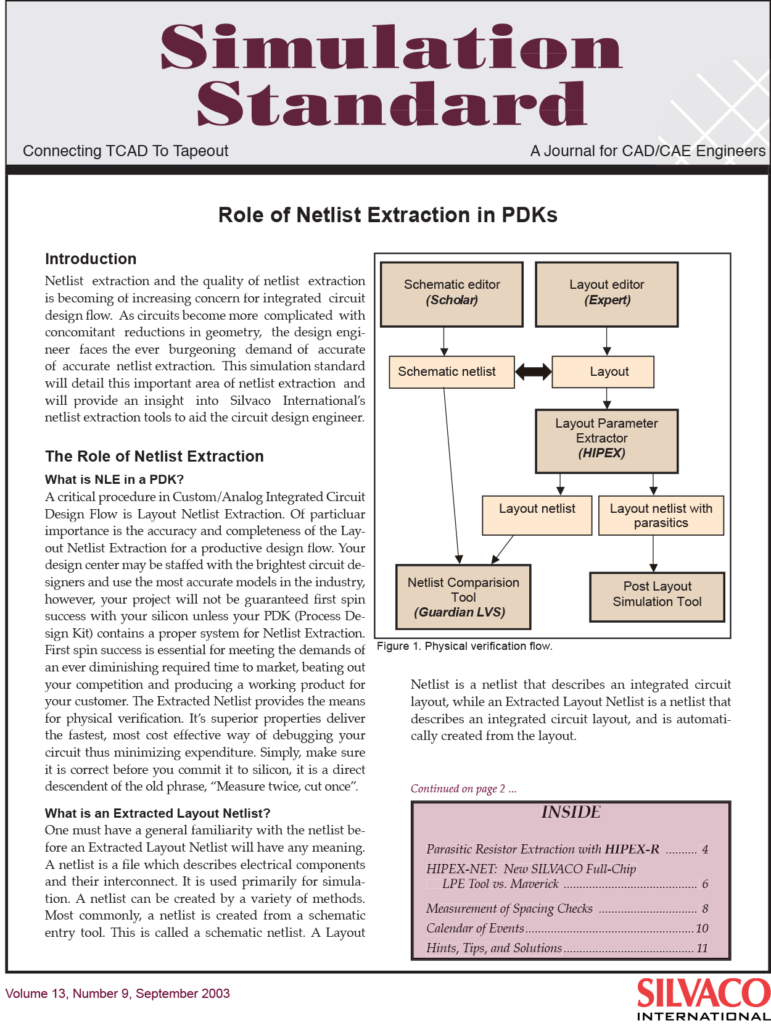

Role of Netlist Extraction in Process Design Kits

Netlist extraction and the quality of netlist extraction is becoming of increasing concern for integrated circuit design flow. As circuits become more complicated with concomitant reductions in geometry, the design engineer faces the ever burgeoning demand of accurate of accurate netlist extraction. This simulation standard will detail this important area of netlist extraction and will provide an insight into Silvaco International’s netlist extraction tools to aid the circuit design engineer.

Parasitic Resistor Extraction with HIPEX-R

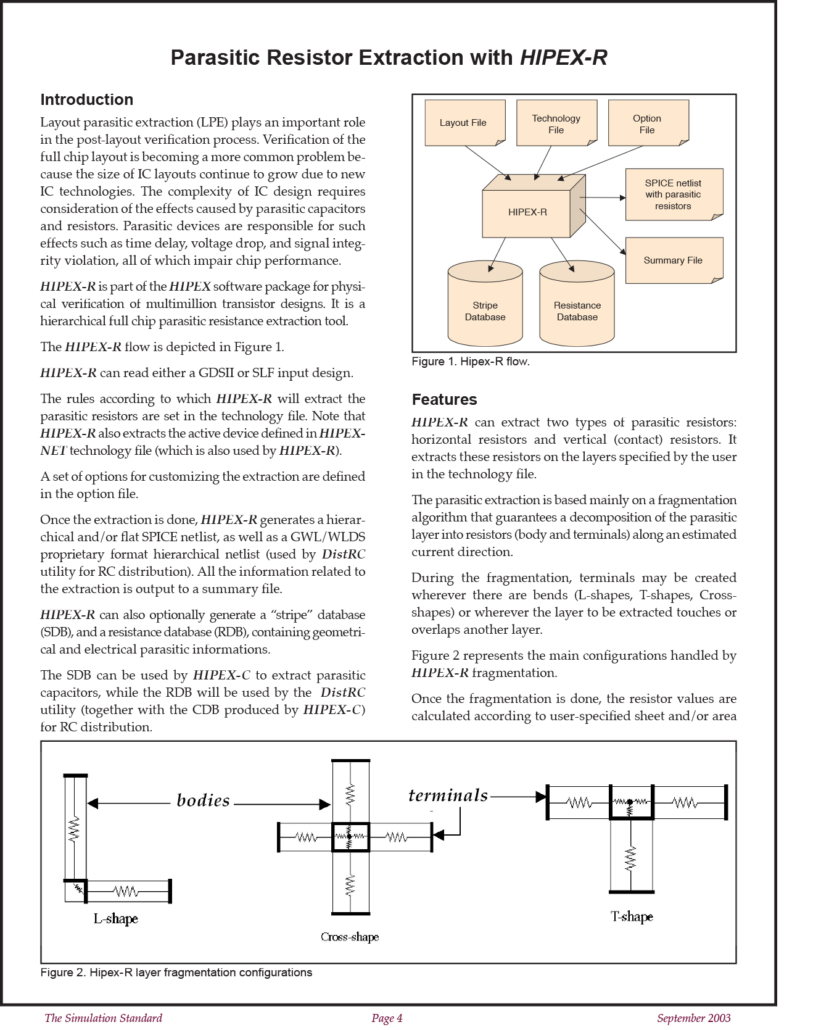

HIPEX-R is part of HIPEX software package for physical verification of multimillion transistor designs. It is a hierarchical full chip parasitic resistance extraction tool.

HIPEX-Net: New SILVACO Full-Chip LPE Tool vs. Maverick

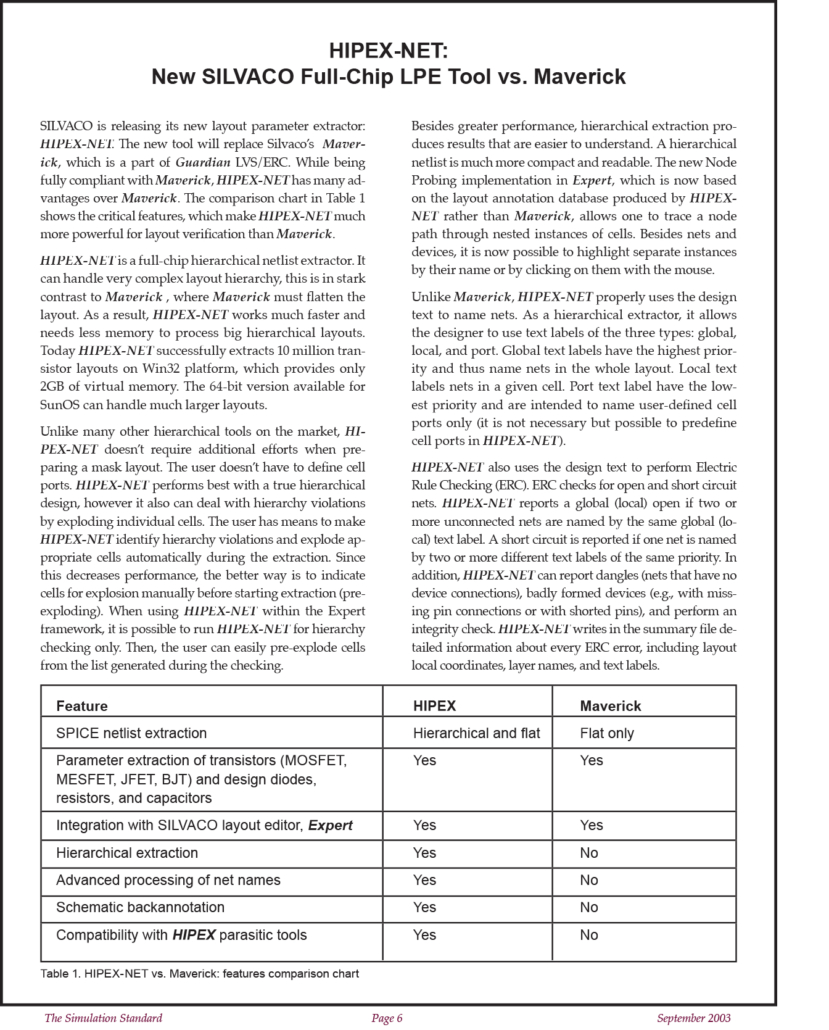

SILVACO is releasing its new layout parameter extractor: HIPEX-NET. The new tool will replace Silvaco’s Maverick, which is a part of Guardian LVS/ERC. While being fully compliant with Maverick, HIPEX-NET has many advantages over Maverick. The comparison chart in Table 1 shows the critical features, which make HIPEX-NET much more powerful for layout verification than Maverick.