Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

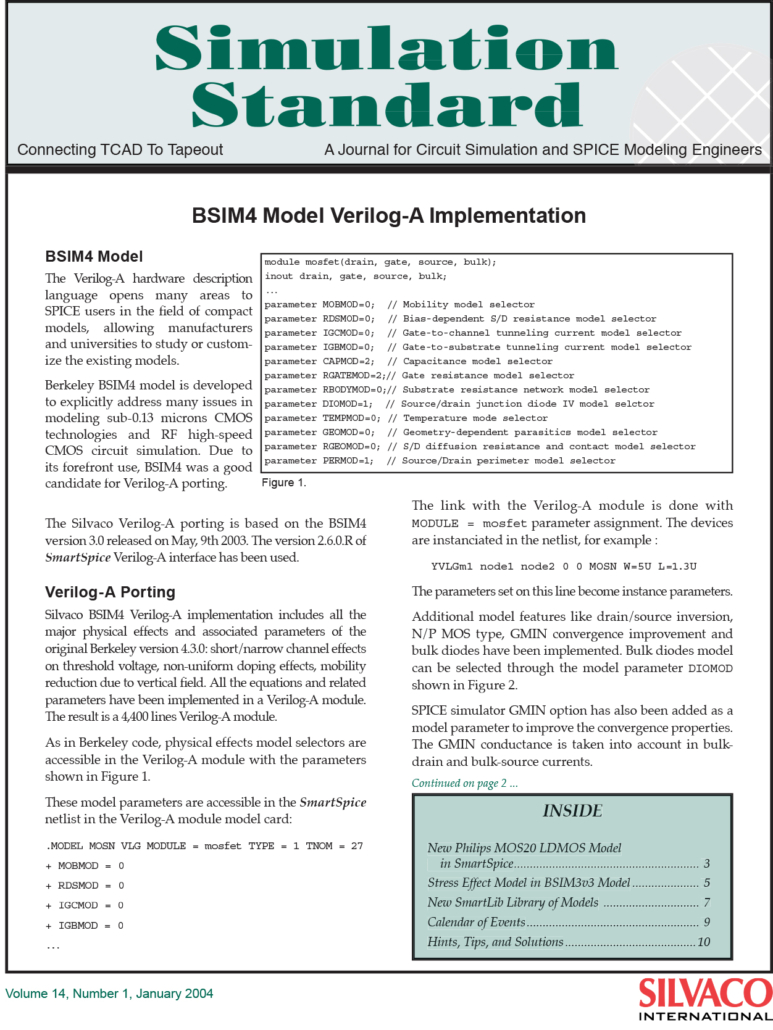

BSIM4 Model Verilog-A Implementation

The Verilog-A hardware description language opens many areas to SPICE users in the field of compact models, allowing manufacturers and universities to study or customize the existing models.

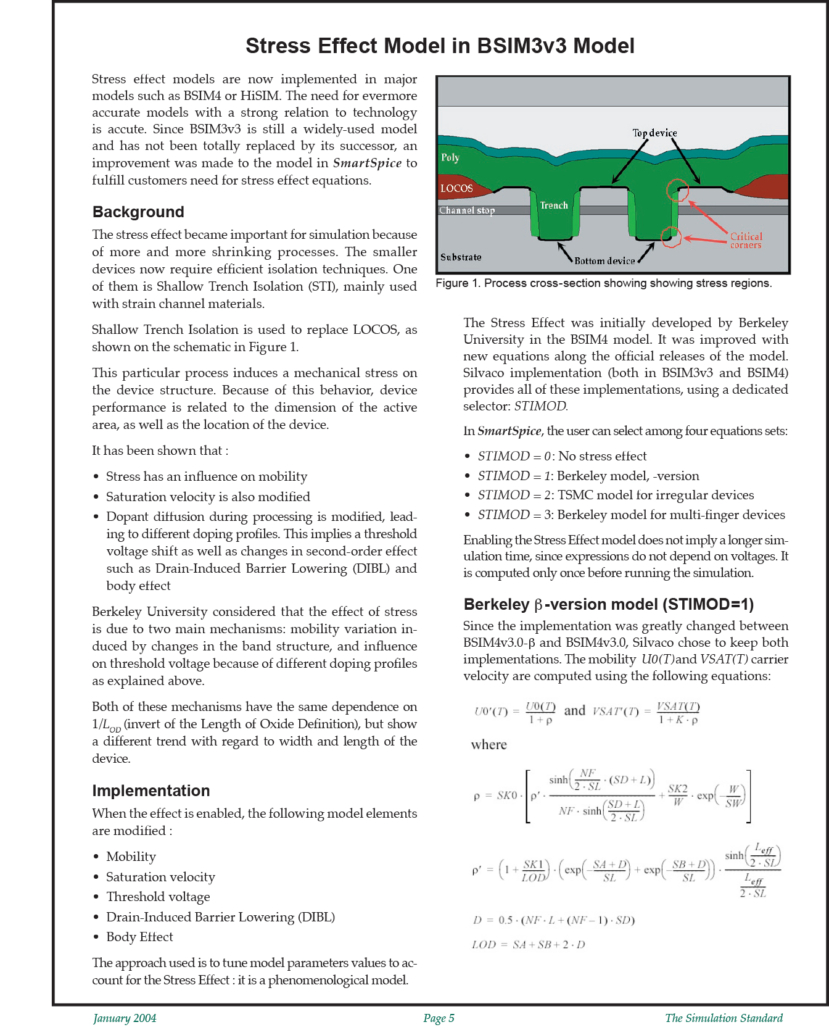

Stress Effect Model in BSIM3v3 Model

Stress effect models are now implemented in major models such as BSIM4 or HiSIM. The need for evermore accurate models with a strong relation to technology is accute. Since BSIM3v3 is still a widely-used model and has not been totally replaced by its successor, an improvement was made to the model in SmartSpice to fulfill customers need for stress effect equations.

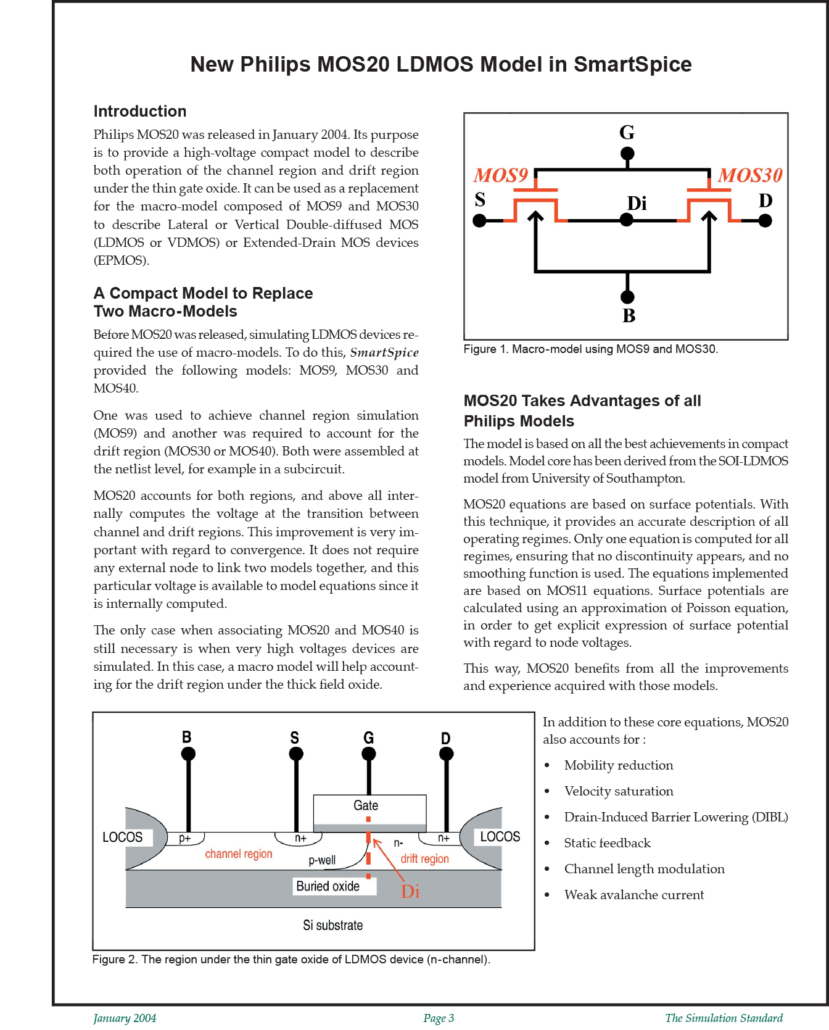

New Philips MOS20 LDMOS Model in SmartSpice

Philips MOS20 was released in January 2004. Its purpose is to provide a high-voltage compact model to describe both operation of the channel region and drift region under the thin gate oxide.

Sometimes I have problem to skip cells when importing cells

Q: Sometimes I have problem to skip cells when importing cells with the same names from reference library. Once we skip one cell, expert will complain other cells already exist in the new library.

A: To process name collisions for several cells when you try to skip some of them:

1. click ‘All Existing’ button in Cell Name Collision dialog. The name of all existing cells become highlighted in grey.

Guardian DRC vs. Other DRC Systems, I

1. Introduction

This article begins a series of articles that describe the compatibility of Guardian DRC system[1] in terms of functionality: command set, syntax and implementation with other leading industrial DRC systems. The purpose of this series is to facilitate the usage of Guardian DRC system by the designers who are already familiar with some other DRC systems.

Schematic Driven Layout

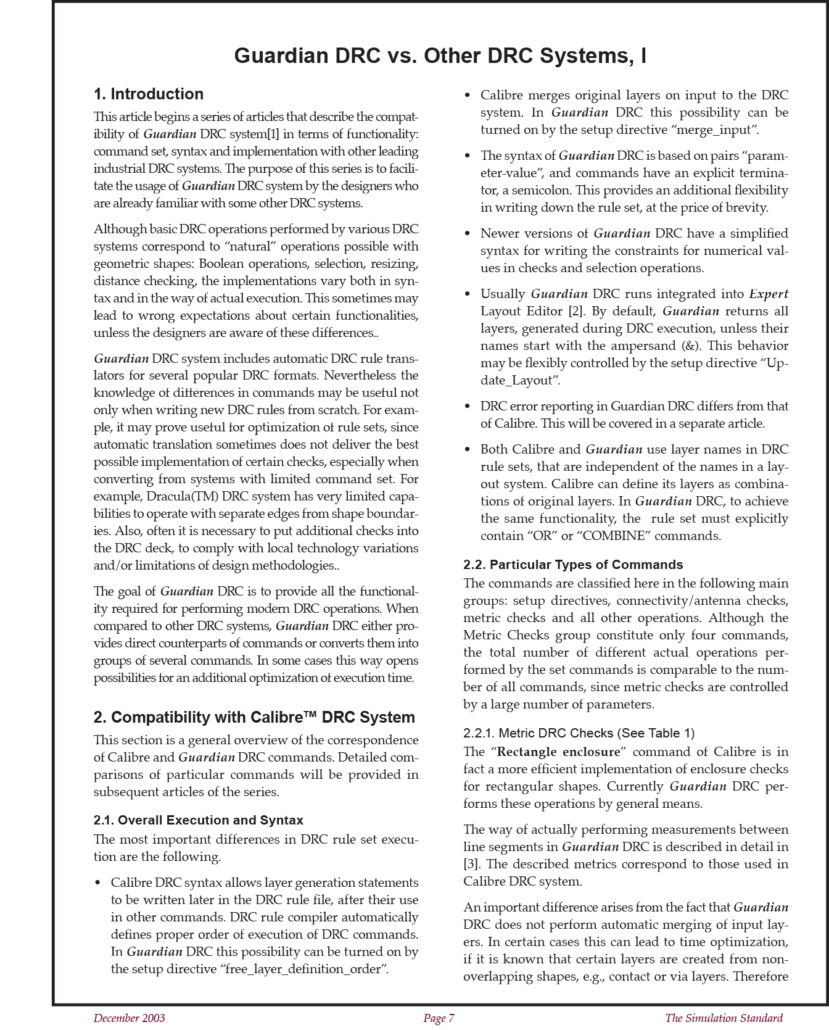

Expert schematic driven layout (SDL) is a CAD tool which increases the productivity of layout design by automating cell generation and providing visual cues to assist the wiring process. In the current implementation, schematic driven layout is used to automatically create IC layouts based on information from a netlist. Cell instances are created from existing cells.