Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

Trapping Effects in the Transient Response of AlGaN/GaN HEMT Devices

In this paper, the transient analysis of an AlGaN/GaN high-electron mobility transistor (HEMT) device is presented. Drain–current dispersion effects are investigated when gate or drain voltages are pulsed. Gate-lag and drain-lag turn-on measurements are analyzed, revealing clear mechanisms of current collapse and related dispersion effects. Numerical 2-D transient simulations considering surface traps effects in a physical HEMT model have also been carried out.

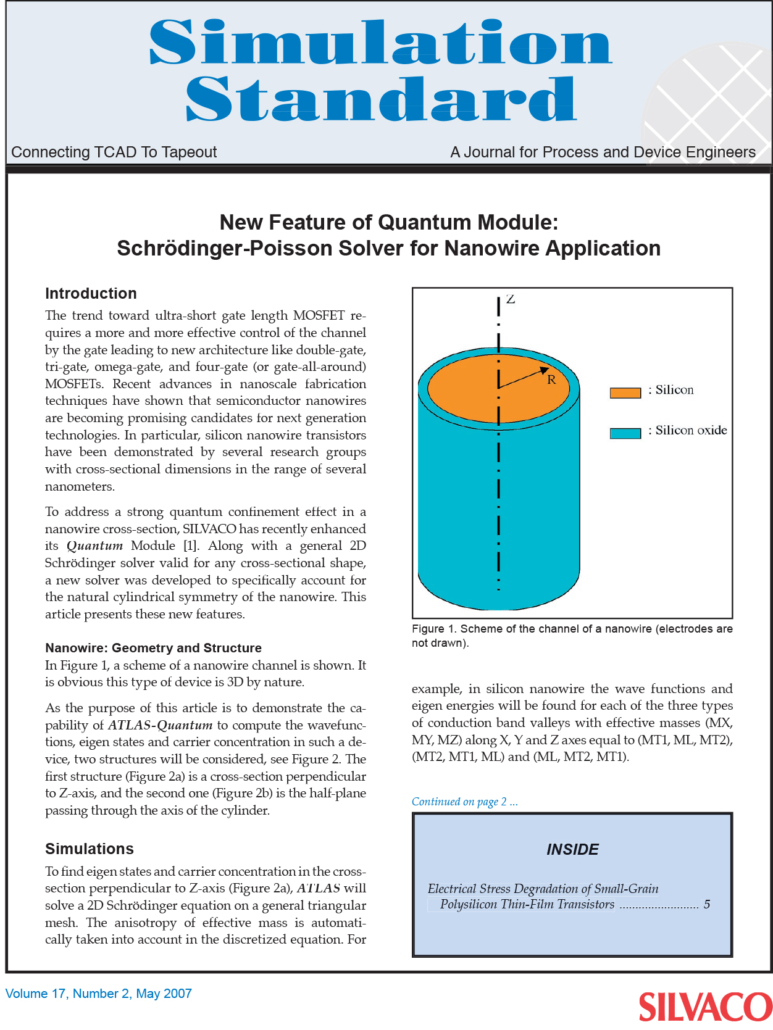

New Feature of Quantum Module: Schrödinger-Poisson Solver for Nanowire Application

Introduction

The trend toward ultra-short gate length MOSFET requires a more and more effective control of the channel by the gate leading to new architecture like double-gate, tri-gate, omega-gate, and four-gate (or gate-all-around) MOSFETs. Recent advances in nanoscale fabrication techniques have shown that semiconductor nanowires are becoming promising candidates for next generation technologies. In particular, silicon nanowire transistors have been demonstrated by several research groups with cross-sectional dimensions in the range of several nanometers.

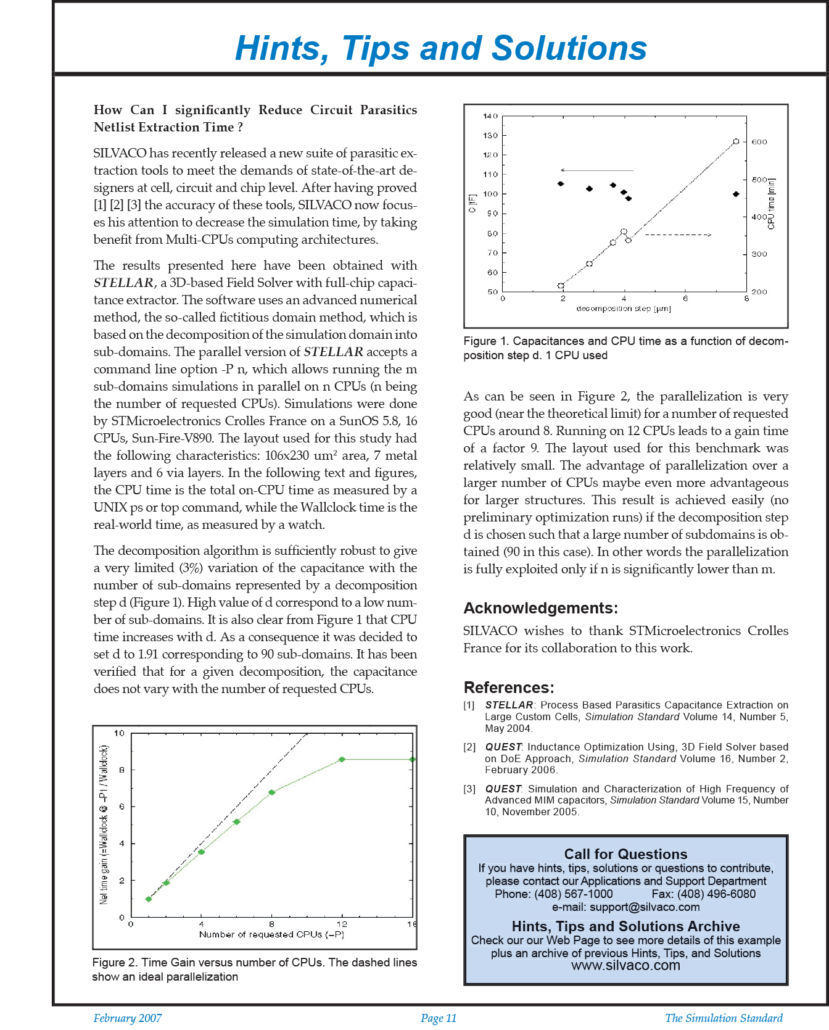

How Can I significantly Reduce Circuit Parasitics Netlist Extraction Time?

How Can I significantly Reduce Circuit Parasitics Netlist Extraction Time?

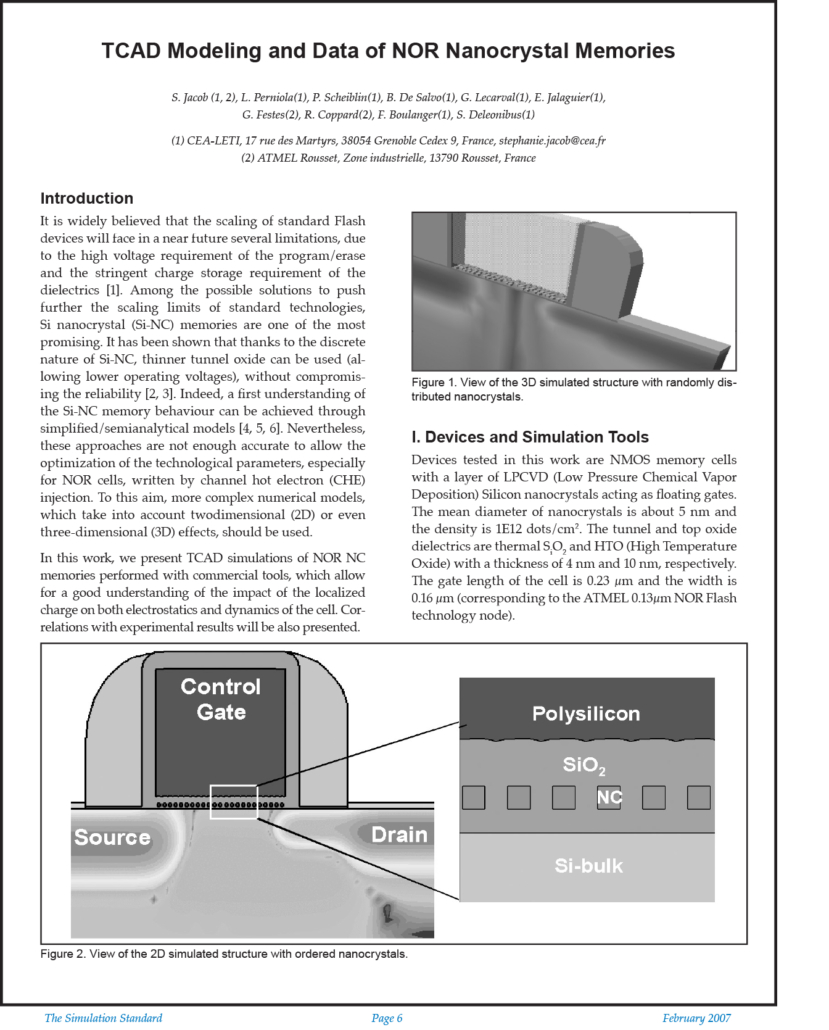

TCAD Modeling and Data of NOR Nanocrystal Memories

Introduction

It is widely believed that the scaling of standard Flash devices will face in a near future several limitations, due to the high voltage requirement of the program/erase and the stringent charge storage requirement of the dielectrics [1]. Among the possible solutions to push further the scaling limits of standard technologies, Si nanocrystal (Si-NC) memories are one of the most promising. It has been shown that thanks to the discrete nature of Si-NC, thinner tunnel oxide can be used (allowing lower operating voltages), without compromising the reliability [2, 3]. Indeed, a first understanding of the Si-NC memory behaviour can be achieved through simplified/semianalytical models [4, 5, 6]. Nevertheless, these approaches are not enough accurate to allow the optimization of the technological parameters, especially for NOR cells, written by channel hot electron (CHE) injection. To this aim, more complex numerical models, which take into account twodimensional (2D) or even three-dimensional (3D) effects, should be used.

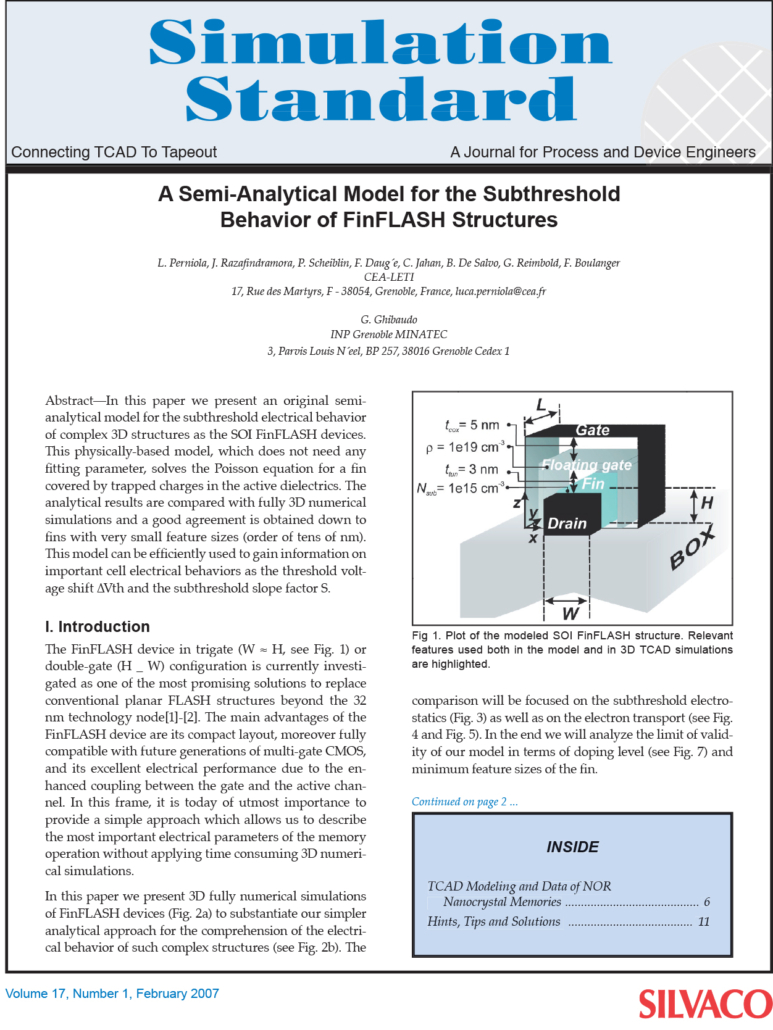

A Semi-Analytical Model for the Subthreshold Behavior of FinFLASH Structures

Abstract

In this paper we present an original semi-analytical model for the subthreshold electrical behavior of complex 3D structures as the SOI FinFLASH devices. This physically-based model, which does not need any fitting parameter, solves the Poisson equation for a fin covered by trapped charges in the active dielectrics. The analytical results are compared with fully 3D numerical simulations and a good agreement is obtained down to fins with very small feature sizes (order of tens of nm). This model can be efficiently used to gain information on important cell electrical behaviors as the threshold voltage shift Vth and the subthreshold slope factor S.

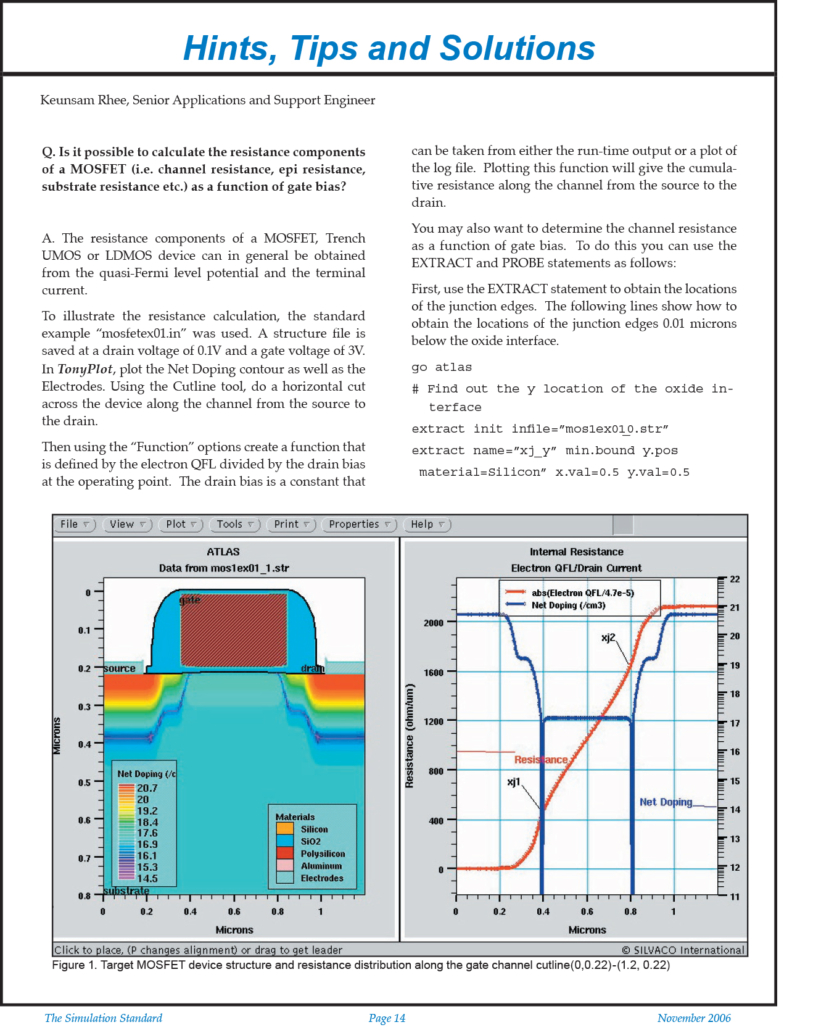

Is it possible to calculate the resistance components of a MOSFET

Q. Is it possible to calculate the resistance components of a MOSFET (i.e. channel resistance, epi resistance, substrate resistance etc.) as a function of gate bias?