Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

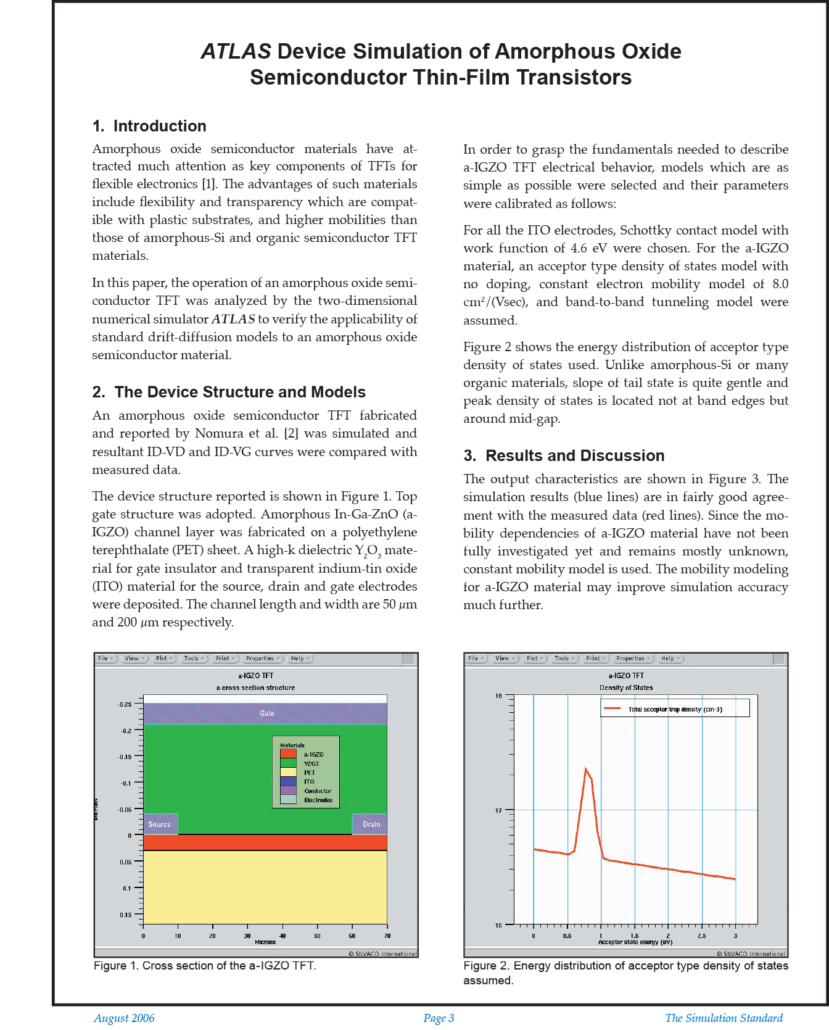

Atlas Device Simulation of Amorphous Oxide Semiconductor Thin-Film Transistors

1. Introduction

Amorphous oxide semiconductor materials have attracted much attention as key components of TFTs for flexible electronics [1]. The advantages of such materials include flexibility and transparency which are compatible with plastic substrates, and higher mobilities than those of amorphous-Si and organic semiconductor TFT materials.

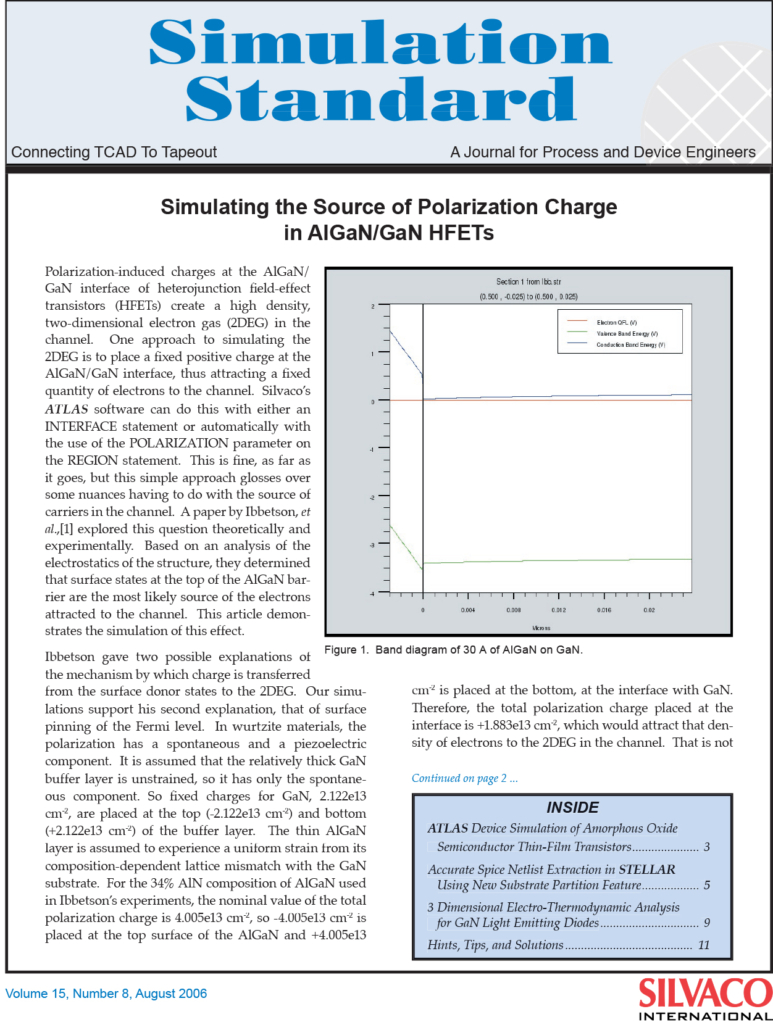

Simulating the Source of Polarization Charge in AlGaN/GaN HFETs

Polarization-induced charges at the AlGaN/GaN interface of heterojunction field-effect transistors (HFETs) create a high density, two-dimensional electron gas (2DEG) in the channel. One approach to simulating the 2DEG is to place a fixed positive charge at the AlGaN/GaN interface, thus attracting a fixed quantity of electrons to the channel. Silvaco’s ATLAS software can do this with either an INTERFACE statement or automatically with the use of the POLARIZATION parameter on the REGION statement. This is fine, as far as it goes, but this simple approach glosses over some nuances having to do with the source of carriers in the channel. A paper by Ibbetson, et al.,[1] explored this question theoretically and experimentally.

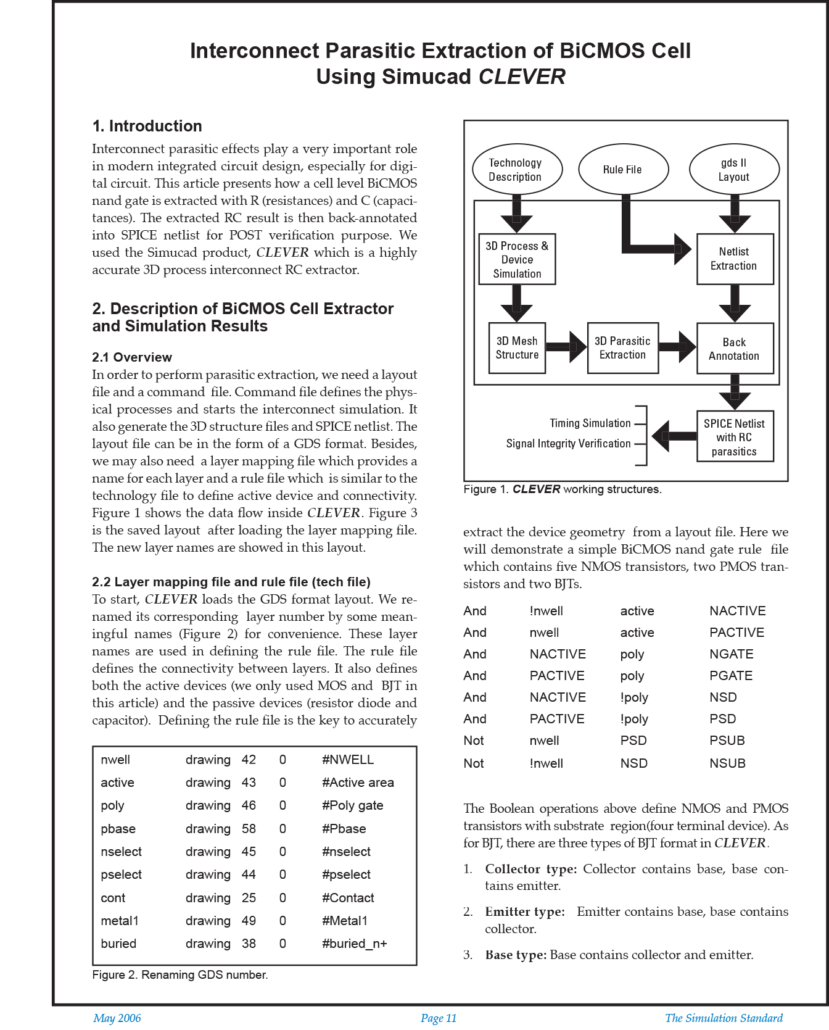

Interconnect Parasitic Extraction of BiCMOS Cell Using Silvaco Clever

Interconnect parasitic effects play a very important role in modern integrated circuit design, especially for digital circuit. This article presents how a cell level BiCMOS nand gate is extracted with R (resistances) and C (capacitances). The extracted RC result is then back-annotated into SPICE netlist for POST verification purpose. We used the Silvaco product, CLEVER which is a highly accurate 3D process interconnect RC extractor.

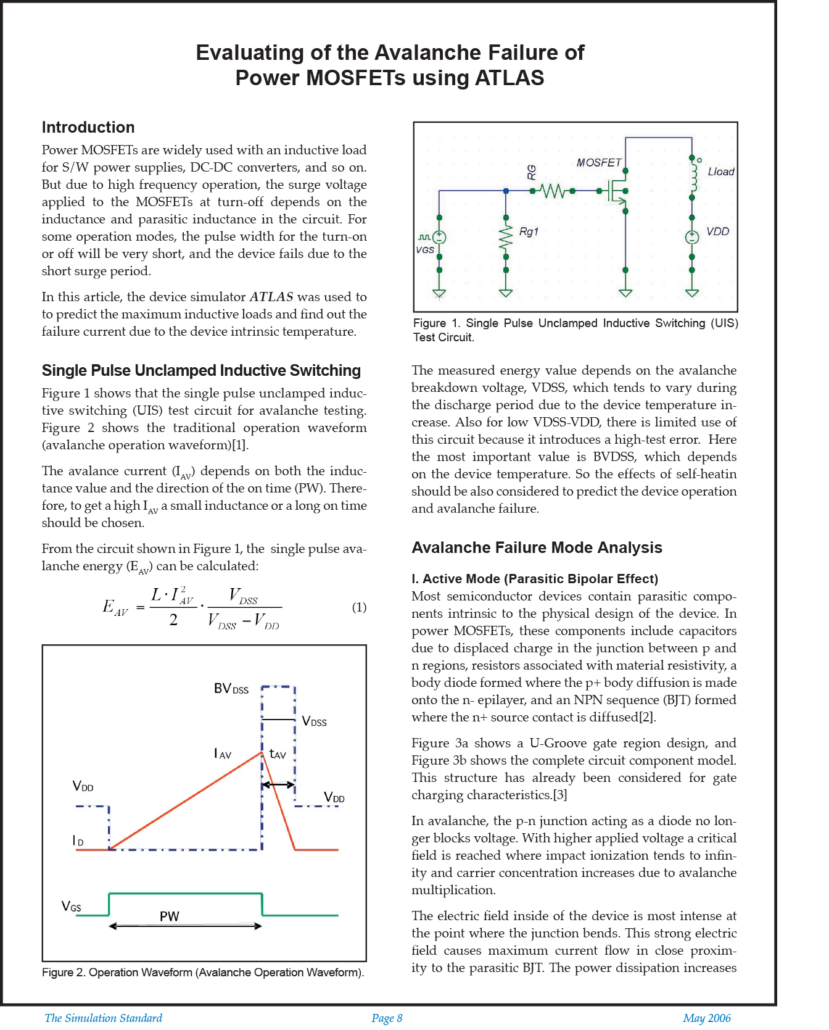

Evaluating of the Avalanche Failure of Power MOSFETs using Atlas

Introduction

Power MOSFETs are widely used with an inductive load for S/W power supplies, DC-DC converters, and so on. But due to high frequency operation, the surge voltage applied to the MOSFETs at turn-off depends on the inductance and parasitic inductance in the circuit. For some operation modes, the pulse width for the turn-on or off will be very short, and the device fails due to the short surge period.

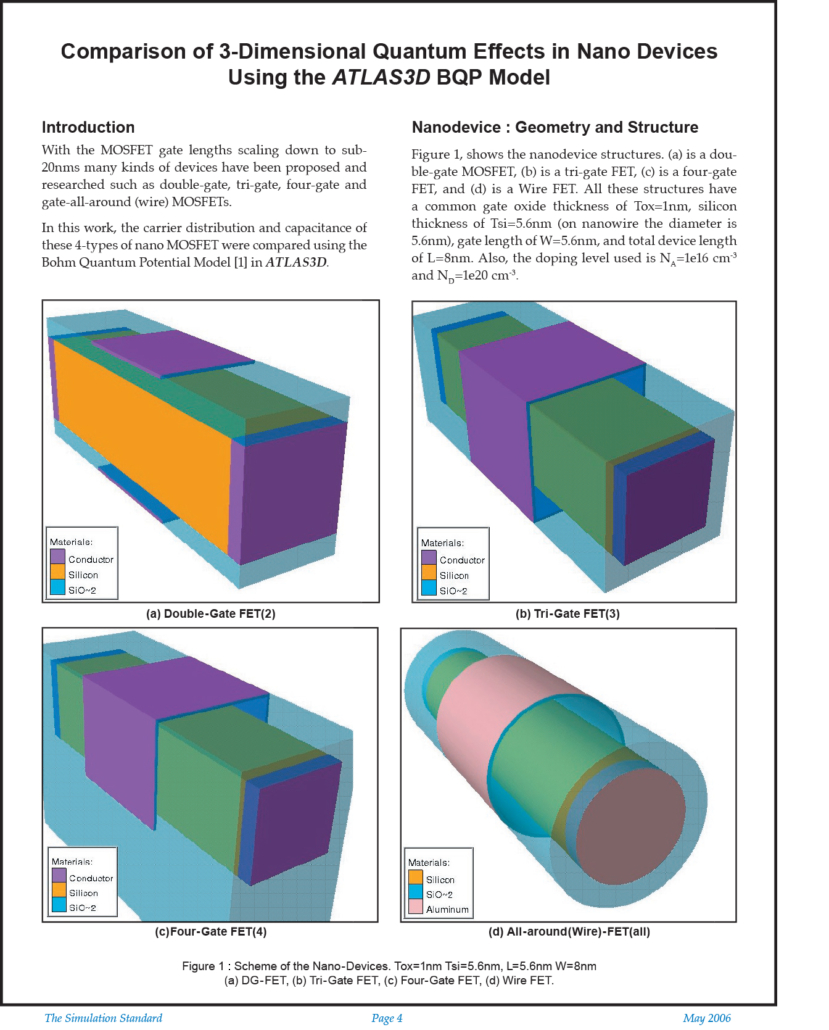

Comparison of 3-Dimensional Quantum Effects in Nano Devices Using the Atlas 3D BQP Model

Introduction

With the MOSFET gate lengths scaling down to sub-20nms many kinds of devices have been proposed and researched such as double-gate, tri-gate, four-gate and gate-all-around (wire) MOSFETs.

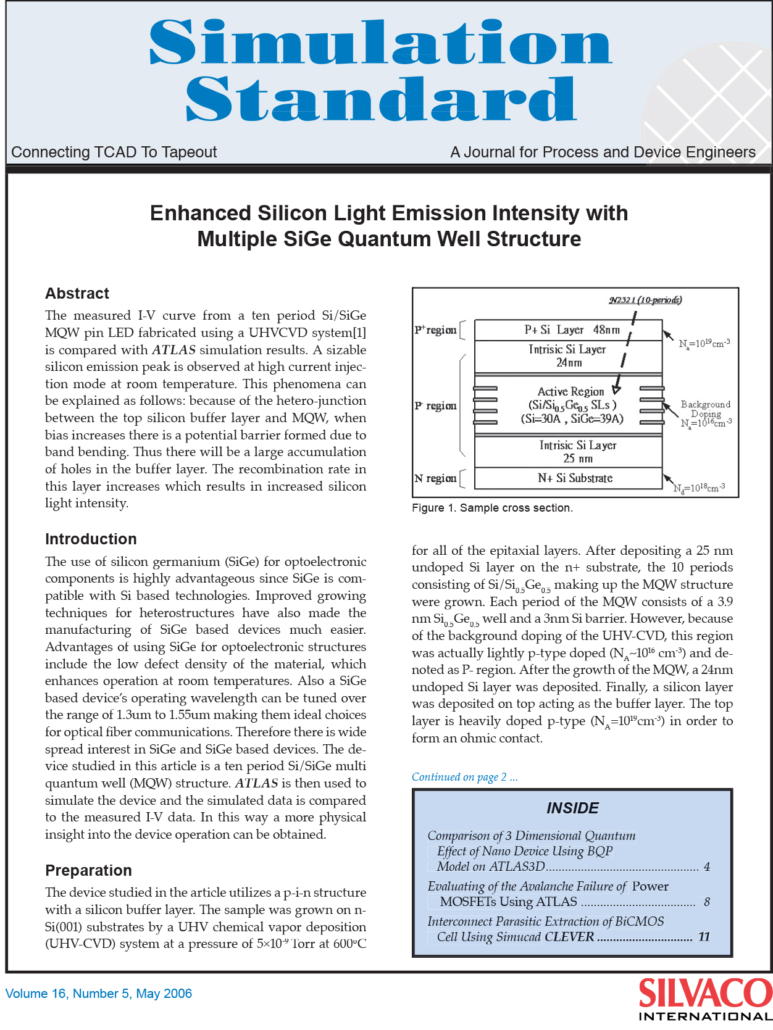

Enhanced Silicon Light Emission Intensity with Multiple SiGe Quantum Well Structure

Abstract

The measured I-V curve from a ten period Si/SiGe MQW pin LED fabricated using a UHVCVD system is compared with ATLAS simulation results. A sizable silicon emission peak is observed at high current injection mode at room temperature. This phenomena can be explained as follows: because of the hetero-junction between the top silicon buffer layer and MQW, when bias increases there is a potential barrier formed due to band bending. Thus there will be a large accumulation of holes in the buffer layer. The recombination rate in this layer increases which results in increased silicon light intensity.