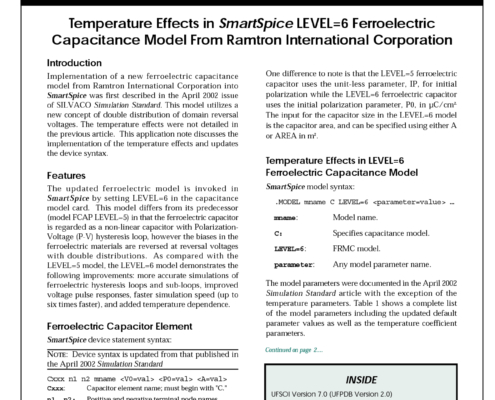

Temperature Effects in SmartSpice LEVEL=6 Ferroelectric Capacitance Model From Ramtron

Implementation of a new ferroelectric capacitance model from Ramtron International Corporation into SmartSpice was first described in the April 2002 issue of Silvaco Simulation Standard. This model utilizes a new concept of double distribution of domain reversal voltages. The temperature effects were not detailed in the previous article. This application note discusses the implementation of the temperature effects and updates the device syntax.

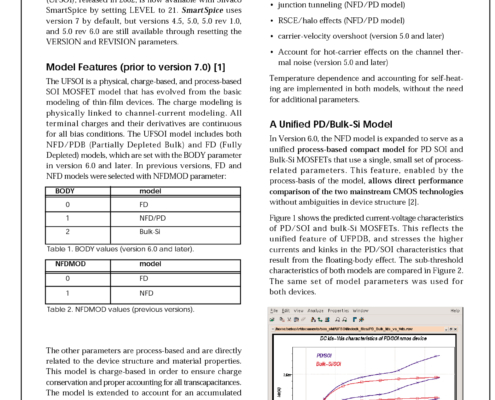

UFSOI V7.0 (UFPDB V2.0) Model Released in SmartSpice

Version 7.0 of the University of Florida Silicon-On-Insulator (UFSOI), released in 2002, is now available with Silvaco SmartSpice by setting LEVEL to 21. SmartSpice uses version 7 by default, but versions 4.5, 5.0, 5.0 rev 1.0, and 5.0 rev 6.0 are still available through resetting the VERSION and REVISION parameters.

Managing SmartSpice / SmartView Simulation Output Raw Files

Silvaco SmartSpice simulation results are typically stored in RAM. Since transient simulations of large circuits often exceed 1GB, a large swap-space partition is required prior to simulation. Constant disk access may dramatically decrease simulation speed, therefore shifting some or all of the load to the system’s memory helps to alleviate this problem.

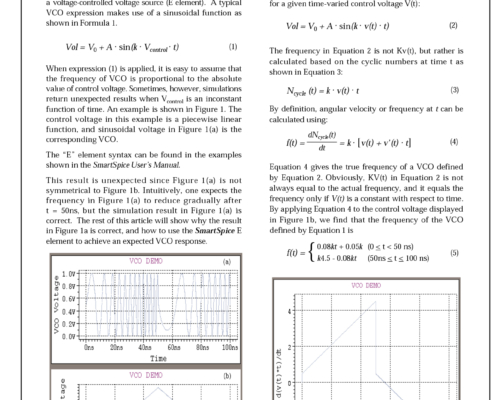

Defining Voltage Controlled Oscillators in SmartSpice

One of the methods to define a Voltage Controlled Oscillator (VCO) in a SPICE simulation is to make use of a voltage-controlled voltage source (E element). A typical VCO expression makes use of a sinusoidal function as shown in Formula 1.

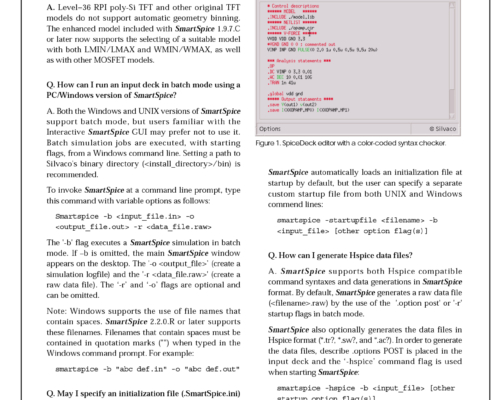

Geometry Binning for TFT models and SmartSpice Tips

Level=36 RPI poly-Si TFT and other original TFT models do not support automatic geometry binning. The enhanced model included with SmartSpice 1.9.7.C or later now supports the selecting of a suitable model with both LMIN/LMAX and WMIN/WMAX, as well as with other MOSFET models.

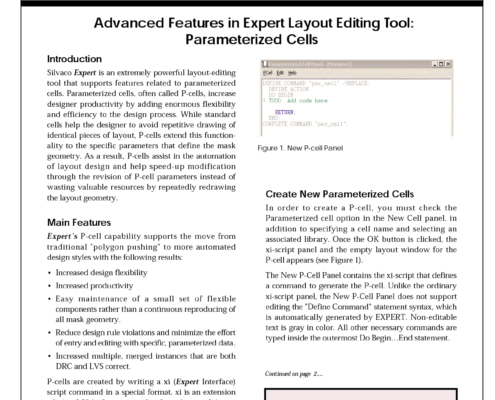

Advanced Features in Expert Layout Editing Tool: Parameterized Cells

Silvaco Expert is an extremely powerful layout-editing tool that supports features related to parameterized cells. Parameterized cells, often called P-cells, increase designer productivity by adding enormous flexibility and efficiency to the design process. While standard cells help the designer to avoid repetitive drawing of identical pieces of layout, P-cells extend this functionality to the specific parameters that define the mask geometry. As a result, P-cells assist in the automation of layout design and help speed-up modification through the revision of P-cell parameters instead of wasting valuable resources by repeatedly redrawing the layout geometry.

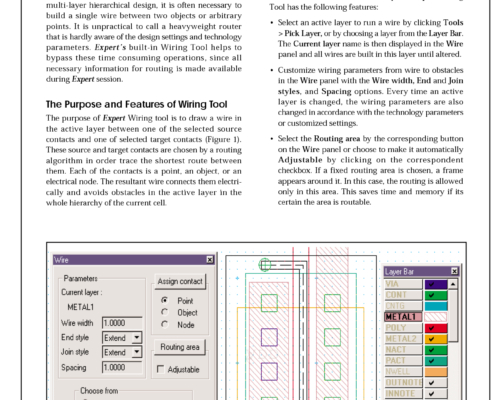

Expert Wiring Tool: Router at Hand

Modern complex circuit designs require automatic router functionality in circuit layout editors. In multi-layer hierarchical design, it is often necessary to build a single wire between two objects or arbitrary points. It is unpractical to call a heavyweight router that is hardly aware of the design settings and technology parameters. Expert’s built-in Wiring Tool helps to bypass these time consuming operations, since all necessary information for routing is made available during Expert session.

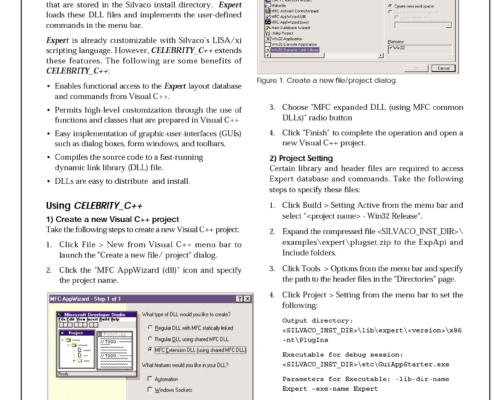

C++ Language Interface for Expert Layout Editor

The C++ interface for Silvaco’s Expert layout tool, is now an exclusive customization language that expands the tool’s handling of high-level customization, such as a design application working with Expert’s database. Users of the interface develop dynamic link libraries (DLLs) with Microsoft Visual C++ that are stored in the Silvaco install directory. Expert loads these DLL files and implements the user-defined commands in the menu bar.

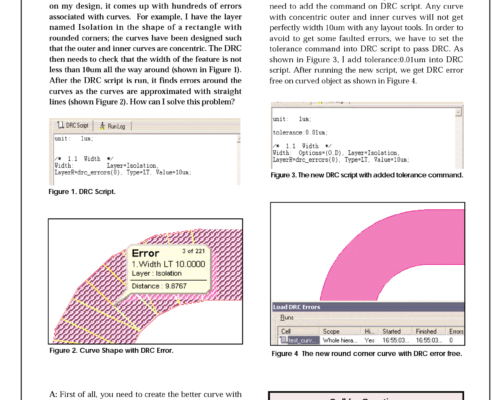

Running a DRC Check on a Design with Round Curves

After I create my round curve and run a DRC check on my design, it comes up with hundreds of errors associated with curves. For example, I have the layer named Isolation in the shape of a rectangle with rounded corners; the curves have been designed such that the outer and inner curves are concentric. The DRC then needs to check that the width of the feature is not less than 10um all the way around (shown in Figure 1). After the DRC script is run, it finds errors around the curves as the curves are approximated with straight lines (shown Figure 2). How can I solve this problem?

Simulating Boron Diffusion in Silicon Germanium

The silicon germanium heterojunction bipolar transistor (SiGe HBT) is a promising technology for combining the operating speed of compound material devices with the production capability of bulk silicon. The presence of a narrower-bandgap material in the base region where most of the bandgap offset occurs in the valence band, creates an energy well for holes. With the lower energy barrier, a lower hole current density can be obtained for a given electron current density increasing the transistor’s gain [1]. Thus the base can then be highly doped, greatly increasing high frequency performance whilst still retaining a reasonable gain. For this reason, the diffusion of boron in SiGe is of great interest.