Utmost IV Quick-Start 모델 최적화 템플릿

2020년 3월 13일 | 2:00am-2:30am (한국 시각)

UTMOST IV: Quick-Start Optimization Templates에서 사용할 수 있는 새로운 기능을 소개합니다. 이 기능은 사용자가 데이터를 기반으로 특정 모델에 대한 최적화 프로젝트를 신속하게 생성할 수 있는 기능입니다. 따라서 SPICE 모델링 경험이 거의 없더라도, 사용자의 생산성을 크게 향상시킬 수 있습니다.

Jivaro 기생성분 추출로 회로 시뮬레이션의 시간 단축 실현

2020년 1월 17일 | 3:00am-3:30am - (한국 시각)

Jivaro에 대한 간략한 소개 후, 더 나은 넷리스트 감소를 위해 필요한 기능과 제어 기법을 제시하여 시뮬레이션 흐름을 개선하기 위한 방법론을 살펴봅니다.

기생성분 감축

Jivaro Parasitic Reduction for Fast, Accurate Simulation

Jivaro is a unique stand-alone solution dedicated to the reduction of parasitic networks. It helps back-end verification teams speed up post-layout SPICE simulation of huge extracted parasitic circuits, while keeping high accuracy.

회로 시뮬레이션

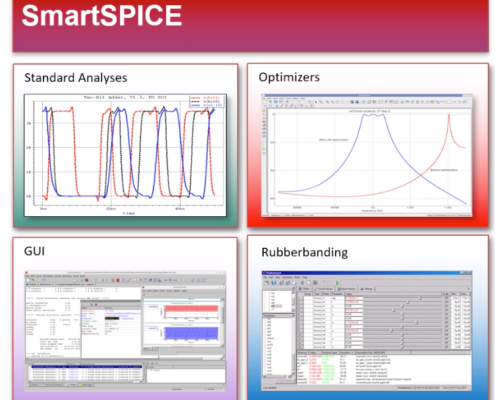

SmartSpice Circuit Simulator

Silvaco’s SmartSpice™ is a high performance parallel SPICE simulator that delivers industry leading accuracy. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes.

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Erick Castellon

/wp-content/uploads/2019/11/silvaco-logo.png

Erick Castellon2019-10-01 17:26:502024-10-21 05:20:14공정 변동 및 수율 분석

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Erick Castellon

/wp-content/uploads/2019/11/silvaco-logo.png

Erick Castellon2019-10-01 17:26:502024-10-21 05:20:14공정 변동 및 수율 분석

기생성분 감축 및 분석

Jivaro is a unique stand-alone solution dedicated to the reduction of parasitic networks. It helps back-end verification teams speed up post-layout SPICE simulation of huge extracted parasitic circuits, while keeping high accuracy.

Viso analyzes the electrical properties of RC parasitic networks which crucially impact circuit behavior in nanometer processes. These impacts affect circuit gain, delay, maximum clock rate, cross-coupling, level of ESD protection and other features, which can cripple a design. Viso’s parasitics-focused approach enables quick analysis of interconnect in order to pinpoint problems. It provides timing estimation and accurate comparison of different extracted netlists.

Belledonne is used for layout comparison via extracted netlist. It compares two different extracted netlists and is mainly used for layout parasitic extraction (LPE) flow qualification.

아날로그 시뮬레이션

Silvaco’s SmartSpice is a high performance parallel SPICE simulator that delivers industry leading accuracy. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes. It uses an intelligent architecture deploying multiple solvers, stepping algorithms and computation techniques. The result is accurate, robust convergence and industry leading performance and capacity – over 8 million active devices. It is compatible with HSPICE® and Spectre® for netlists, models, analysis features, and results – plus large libraries of calibrated device models are available. Featuring integration with Silvaco Gateway schematic editor and SmartView waveform viewer, SmartSpice fits seamlessly into front-end analog IC design flows.

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Erick Castellon

/wp-content/uploads/2019/11/silvaco-logo.png

Erick Castellon2019-10-01 17:25:482023-01-30 00:45:17SPICE 모델 생성

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Erick Castellon

/wp-content/uploads/2019/11/silvaco-logo.png

Erick Castellon2019-10-01 17:25:482023-01-30 00:45:17SPICE 모델 생성 /wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2019-09-16 00:00:002025-05-09 01:54:55실바코와 HDL Design House가 제휴하여, 아날로그 및 디지털 IC 디자인 서비스를 제공

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2019-09-16 00:00:002025-05-09 01:54:55실바코와 HDL Design House가 제휴하여, 아날로그 및 디지털 IC 디자인 서비스를 제공

Verilog-A를 사용한 SPICE 모델링: 원리 및 실제 기술

2019년 6월 26일 | 2:00am-2:30am (한국 시각)

Verilog-A으로 SPICE 컴팩트 모델을 구현하기 위한 전문적인 가이드를 소개합니다.