エンベデッド・メモリ・コンパイラIP

シルバコは、HPCおよびAIメモリ・ソリューションの需要に応えるため、業界初のプロセッサ速度に対応する、キャッシュ・メモリ・コンパイラを提供します。シルバコの超高速キャッシュ・メモリは、先進のキャッシュ・アーキテクチャとロジック・ルールに対応したビットセルを特徴とする、適応性のあるノンコヒーレント・キャッシュのIPです。このアーキテクチャは、システム性能、スケーラビリティ、電力効率、データ局所性、アプリケーション応答性、コスト最適化、市場競争力を高め、独自のビジネス価値を提供します。

シルバコはまた、高性能、低消費電力、高密度を実現するアーキテクチャを備えた組み込みメモリ・コンパイラも幅広く提供しています。シルバコのソリューションにより、設計者は性能、電力効率、空間的配慮の間で適切なバランスを取ることができます。

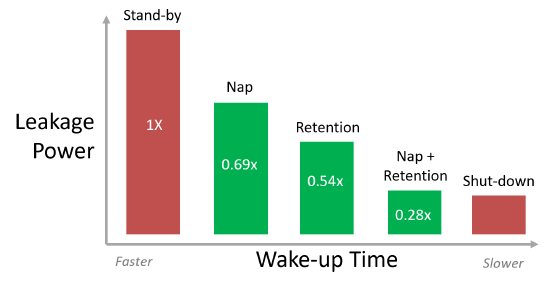

最先端の電力管理機能を活用した当社のメモリ・コンパイラは、最も困難な低消費電力、低リーク、低電圧の設計仕様に対応できます。

Learn How SilTerra Uses Cello and Viola for Standard Cells and I/O Library Optimization and Characterization

Learn About Silvaco’s AMBA AHB Subsystems and How to Customize, Secure, and Verify

Managing the Complexity of FinFET Standard Cell Layout with Cello

Designing with Silvaco’s Octal SPI Memory Controller with Advanced Memory Support for IoT Systems

Achieving Extreme Low Power IoT Designs with Silvaco’s 55LPx Foundation IP Solution