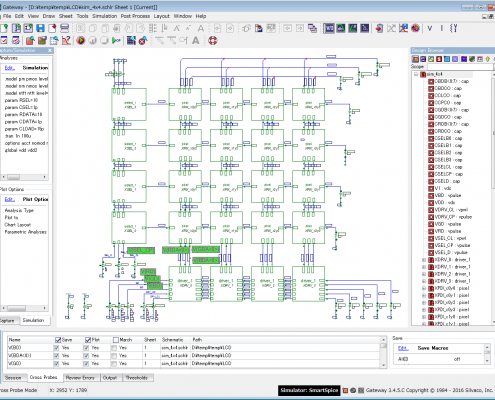

Gateway スケマティック・エディタ

Gatewayは、使いやすさと視認性を追求した回路設計環境を提供する階層スケマティック・エディタです。アナログ、デジタル、ミックスドシグナル、RFデザインを設計するための様々な機能と環境を提供しています。

はじめに

Gatewayは、直感的な編集機能により高い作業効率を実現する環境を提供し、大規模、多階層、フラットなど様々なデザインに対応するツールです。既存のネットリストからシンボルを自動生成する機能等、業界標準の各種ネットリストおよびファイル・フォーマットをサポートしています。

Gatewayは、他のシルバコ・ツールとの強力なインタフェースを搭載し、回路図編集、シミュレーション、レイアウト、および物理検証のためのさまざまな編集モードを持っています。SmartSpice、Silos、SmartView、Atlas、Victory Device、Expert、Guardian LVSとの連携が可能です。

Gatewayは強力なスクリプト機能を備えており、個々の設計者および設計チームの具体的なニーズに合わせてインタフェースおよび機能をカスタマイズできます。

特長

- 階層構造、Multi-View、複数シートに対応し、大規模で複雑な設計に対応可能

- ワイヤ、バス、信号の分岐、信号のマージによるEdit-in-Place機能

- ワイヤ間接続、ワイヤのピンへの接続、名前による間接的な接続、およびグローバル接続が可能

- 波形表示と回路図間のクロス・プロービング機能

- 階層構造によるネット/セル情報表示機能を備え、全階層を通した配線の接続をトレース可能

- カスタマイズ可能なルール・チェック機能により、回路作成時のルール違反やネットリストの違反の検出、表示が可能

- デバイス・パラメータ、DCバイアス、およびしきい値の表示に対応

利点

- 直感的に操作可能な使いやすい設計環境により、設計の作成・編集作業の迅速化を実現

- さまざまな設計フローと用途に対応した各種ネットリストを1つの回路図から生成でき、複数のネットリスト形式をサポートするインポート/エクスポート機能を使用可能

- バス名、インスタンス名、およびノード名に関する先進の名称管理システムにより、大規模階層設計もフラットな設計も容易に概念化可能

用途

- アナログ/デジタル・ブロック、ミックスドシグナル、RF、スタンダード・セル、IOなど

技術仕様

- 対応ネットリスト・フォーマット

- SPICE

- CDL

- NDL

- Verilog IEEE 1364

- 対応シミュレーション環境

- SmartSpice

- HSPICE®

- Silos

- AtlasやVictory Deviceなどのデバイス・シミュレータ

- OpenAccess、iPDKのサポート

- EDIF 200を介した他社製回路図エディタとの統合を可能にするインタフェース

- JavaScriptを使った先進のスクリプト環境により、200個以上の関数のサポート、メニューとGUIのカスタマイズ、およびユーザ定義のCallbackシンボルの作成が可能

- さまざまなファウンドリに対応したカスタムPDKのサポート(iPDKもサポート。最新のサポート状況については、シルバコまでお問い合わせください)

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

新機能Design Explorerを使ったアナログ回路設計とポストレイアウト・シミュレーション

SmartSpice Signal Integrity 最新機能の紹介

RPI TFTモデルの理解と実装(2)リーク電流モデル