意法半导体:如何使用Silvaco TCAD研究表面缺陷点对SiC器件短路现象的影响

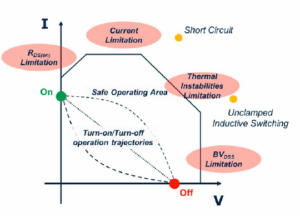

在打开和关闭SiC器件时,器件容易出现异常过载,因此在一些应用中对器件“鲁棒性”有要求,例如需进行短路测试和UIS测试。通过混合电路可以仿真这种过载现象,结合仿真结果和实验结果,可以精确地调整仿真参数,预测动态阶段的电热表现。在本次研讨会中,来自意法半导体的研发人员将为大家介绍对SiC器件短路现象的研究。他们使用Silvaco TCAD仿真软件,研究了位于活动区域的局部缺陷短路对器件产生的影响,包括缺陷点位于不同位置时的情况(平坦的体/漏极界面处、沟道区的SiC/Oxide界面处、以及曲面的体/漏极界面处)以及对位置的敏感性研究。

内容概要

- 宽禁带(WBG)技术和SiC的特性

- SiC MOSFET的开关操作和韧性

- TCAD仿真和器件可靠性

- 表面缺陷点对短路的影响

讲师简介

Salvatore Cascino,SiC研发工程师,意法半导体

Salvatore Cascino目前在意法半导体研发部门工作,专注于碳化硅器件的技术开发。曾就职于欧洲著名的核聚变研究中心——意大利ENEA研究所,参与核聚变部门FTU项目和聚变研究小组的RFX项目。对传感器和射频器件也有丰富的开发经验。Salvatore Cascino拥有巴勒莫大学的物理学学位。

建议参会人员:

半导体器件和工艺工程师、产品经理和工程管理人员。

时间:

圣克拉拉时间:

2024年3月28日 10:00 – 10:30

巴黎时间:

2024年3月28日 11:00 – 11:30

北京时间:

2024年3月28日 10:00 – 10:30

地点: 线上

语言: 英文