Learn How STMicroelectronics Silicon Carbide (SiC) Research Team uses Silvaco TCAD to Analyze the Impact of Surface Defect Dot on Short Circuit Phenomena in SiC Devices

配信開始日: 2024年4月1日

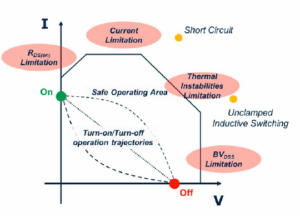

SiCデバイスのスイッチング動作中、デバイスが異常な過負荷状態に達する可能性があります。そのため、アプリケーションによっては「ロバスト性」仕様(短絡試験やUIS試験など)が要求されます。このような過負荷現象は、シミュレーション/実験情報の交換により、mixed-mode回路とシミュレーション・パラメータの正確な調整によってシミュレートすることができます。これにより、動的に電気的・熱的な挙動を予測することができます。一例として、ここでは短絡現象の研究を報告します。シルバコ・ソフトウェアを用いたTCADシミュレーションにより、活性領域に局在する欠陥の短絡現象への影響を調査しました。欠陥ドットが平坦なボディ/ドレイン界面、チャネル領域のSiC/酸化膜界面、湾曲したボディ/ドレイン界面に局在するさまざまなケースを検討し、位置に対する感度も調査しました。

SiCデバイスのスイッチング動作中、デバイスが異常な過負荷状態に達する可能性があります。そのため、アプリケーションによっては「ロバスト性」仕様(短絡試験やUIS試験など)が要求されます。このような過負荷現象は、シミュレーション/実験情報の交換により、mixed-mode回路とシミュレーション・パラメータの正確な調整によってシミュレートすることができます。これにより、動的に電気的・熱的な挙動を予測することができます。一例として、ここでは短絡現象の研究を報告します。シルバコ・ソフトウェアを用いたTCADシミュレーションにより、活性領域に局在する欠陥の短絡現象への影響を調査しました。欠陥ドットが平坦なボディ/ドレイン界面、チャネル領域のSiC/酸化膜界面、湾曲したボディ/ドレイン界面に局在するさまざまなケースを検討し、位置に対する感度も調査しました。

内容

- ワイドバンドギャップ(WBG)技術とSiCの主な特徴

- SiC MOSFETのスイッチング動作と耐久性

- TCADシミュレーションとデバイスの信頼性

- 短絡: 表面欠陥ドットの影響

プレゼンタ

Salvatore Cascino, SiC R&D Engineer, ST Microelectronics

Salvatore Cascino氏は、1970年パレルモ(イタリア)生まれ。University of Palermoで物理学の学位を取得。ENEA(フラスカティ-ローマ)の核融合部門(FTUプロジェクト)およびパドヴァの核融合研究グループ(RFXプロジェクト)に従事。現在はSTMicroelectronics社(カターニア)のR&Dグループに所属し、炭化ケイ素デバイスの技術開発を研究テーマとしている。過去には、センシング・アプリケーションや高周波用デバイスの開発にも従事。

対象:

半導体デバイスおよびプロセスエンジニア、プロダクトマネージャー、エンジニアリング管理者

[日本時間]

開催日時:

2024年3月28日

11:00am JST (10:00 Beijing)

7:00pm JST (11:00 Paris)

2024年3月29日

3:00am JST (10:00 Santa Clara)

(各回、同じ内容になります。)

配信: オンライン

言語: 英語