Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

Hints, Tips and Solutions – Adding Random Noise to Mask Layout

Geometrical module of Victory Process allows the fast and accurate transfer of mask patterns to the structure. However, sometimes it is necessary to emulate the imperfections of physical processes while retaining the speed and accuracy of the geometrical approximation. For example, you may want to test the tolerance of the final device to random fluctuations in structure’s geometry.

Advanced Process and Device 3D TCAD Simulation of Split-Gate Trench UMOSFET

Lower conduction loss and fast switching characteristics for power devices are increasingly required in the more and more energy-conscious world. For the low to medium voltage ranges (12 V ~ 250 V), the split gate structures [1] have become prevalent in the power MOSFET technologies [2-4]. They allow to achieve the best trade-off between the breakdown voltage (BV) and specific on-state resistance (RSP) for the vertical discrete power MOSFETs. Most of these solutions are based on the RESURF (Reduced Surface Field) action of Split-Gate Resurf Stepped Oxide (SG-RSO) along the drift region.

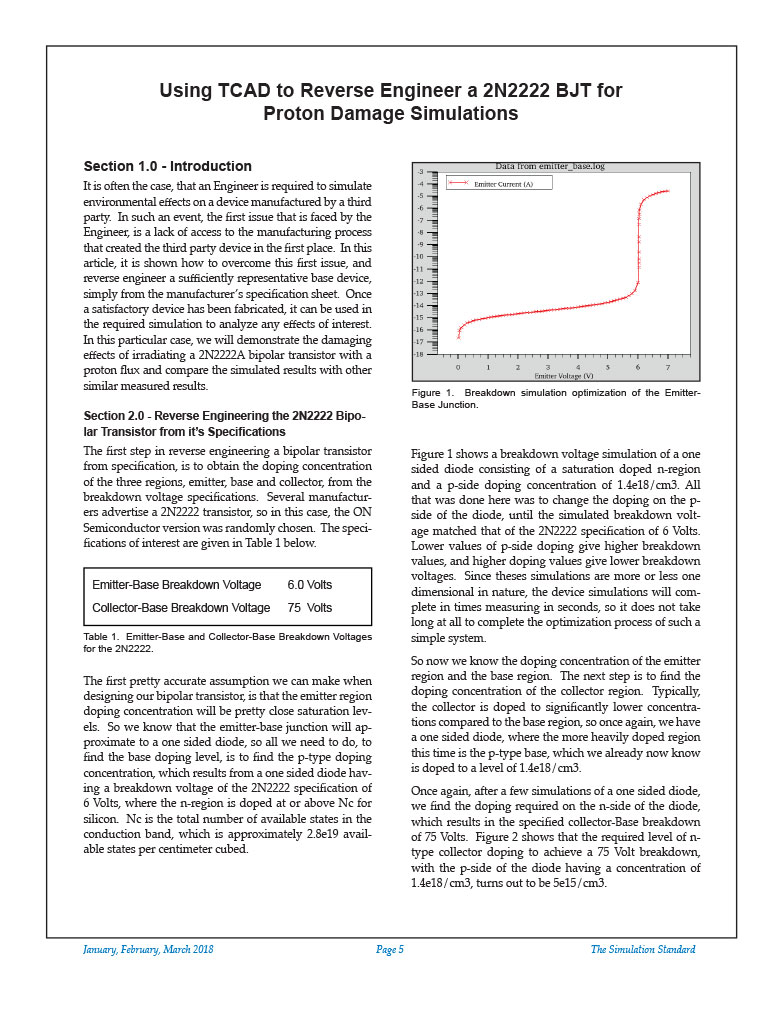

Using TCAD to Reverse Engineer a 2N2222 BJT for Proton Damage Simulations

It is often the case, that an Engineer is required to simulate environmental effects on a device manufactured by a third party. In such an event, the first issue that is faced by the Engineer, is a lack of access to the manufacturing process that created the third party device in the first place. In this article, it is shown how to overcome this first issue, and reverse engineer a sufficiently representative base device, simply from the manufacturer’s specification sheet. Once a satisfactory device has been fabricated, it can be used in the required simulation to analyze any effects of interest. In this particular case, we will demonstrate the damaging effects of irradiating a 2N2222A bipolar transistor with a proton flux and compare the simulated results with other similar measured results.

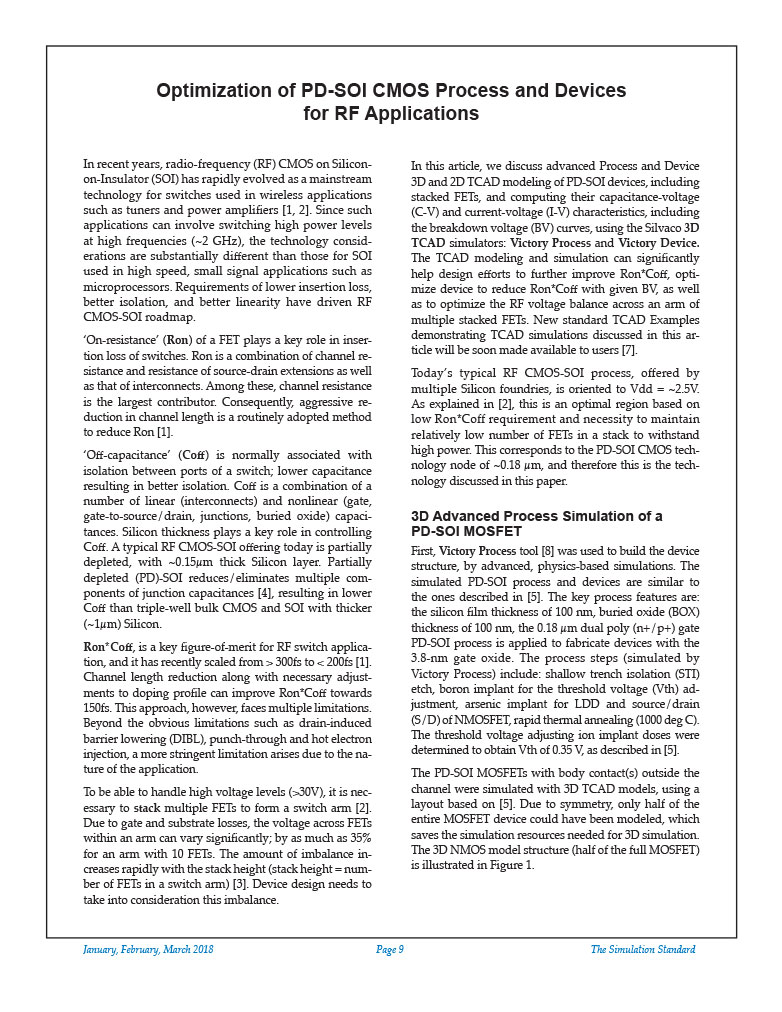

Optimization of PD-SOI CMOS Process and Devices for RF Applications

In recent years, radio-frequency (RF) CMOS on Silicon-on-Insulator (SOI) has rapidly evolved as a mainstream technology for switches used in wireless applications such as tuners and power amplifiers [1, 2]. Since such applications can involve switching high power levels at high frequencies (~2 GHz), the technology considerations are substantially different than those for SOI used in high speed, small signal applications such as microprocessors. Requirements of lower insertion loss, better isolation, and better linearity have driven RF CMOS-SOI roadmap.

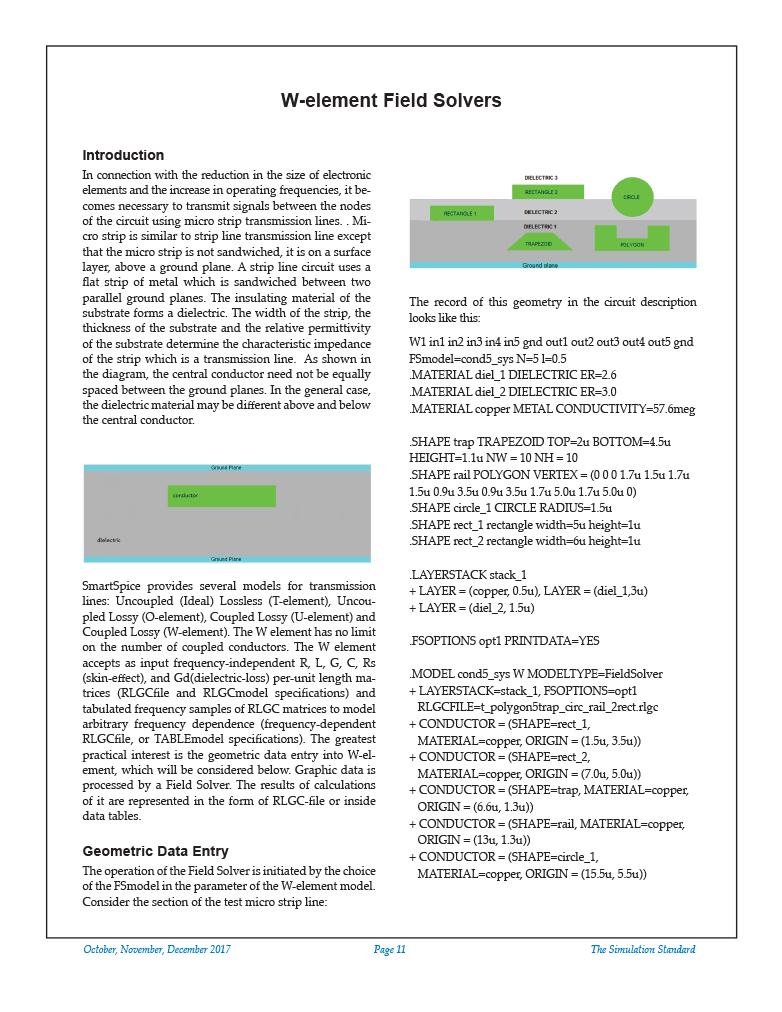

W-element Field Solvers

In connection with the reduction in the size of electronic elements and the increase in operating frequencies, it becomes necessary to transmit signals between the nodes of the circuit using micro strip transmission lines. . Micro strip is similar to strip line transmission line except that the micro strip is not sandwiched, it is on a surface layer, above a ground plane. A strip line circuit uses a flat strip of metal which is sandwiched between two parallel ground planes. The insulating material of the substrate forms a dielectric. The width of the strip, the thickness of the substrate and the relative permittivity of the substrate determine the characteristic impedance of the strip which is a transmission line. As shown in the diagram, the central conductor need not be equally spaced between the ground planes. In the general case, the dielectric material may be different above and below the central conductor.

SmartSpice Shared Mode API

SmartSpice API, shared mode, was developed in order to provide an easy to use solution for products requiring the analog SPICE core engine as an integral part of their functionality. It is a fast and reliable application programming interface used by several SILVACO’s and customer’s tools. The main idea is to allow a client tool to dynamically link with SPICE shared object from pre-installed SmartSpice release package. For convenience, there is a small static library, called ‘testspice’, which can be used to make integration process seamless. In this article we are going to use this library to demonstrate how to use SPICE shared mode API on simple example. The example is ‘testLiteShared.cpp’ can be found with testspice.