Hipex-CRC Parasitic RC-Network Reducer

Introduction

Design of large scale chips requires precise knowledge of interconnect delays. However, detailed analysis of interconnects may quickly become computationally too expensive due to the distributed nature of the networks, and the large number of internal nodes extracted.

HIPEX-CRC is a parasitic RC-network reduction tool able to reduce the huge number of elements produced by major EDA parasitic extractors, including coupling capacitors, and supports main industry standards parasitic formats.

Advanced algorithm behind HIPEX-CRC enables to maintain accuracy within a few percents of Spice. HIPEX-CRC can be directly plugged to the HIPEX suite, but also can be used as a stand-alone tool.

Scattering-Parameter-Based Macromodeling

- HIPEX-CRC allows the user to preprocess the circuit, making a first equivalent reduction by merging serie-parallel elements and removing dangling elements

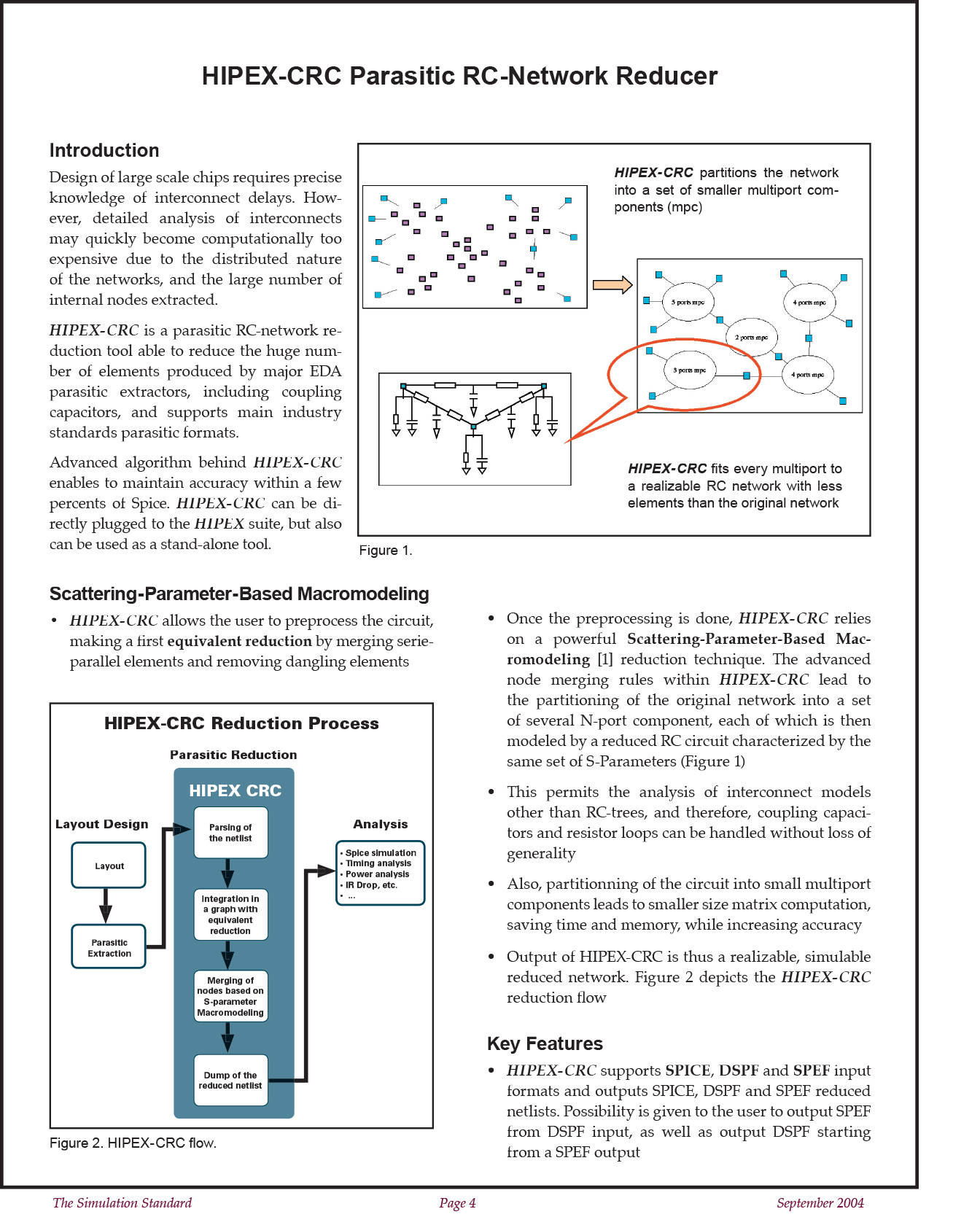

- Once the preprocessing is done, HIPEX-CRC relies on a powerful Scattering-Parameter-Based Macromodeling [1] reduction technique. The advanced node merging rules within HIPEX-CRC lead to the partitioning of the original network into a set of several N-port component, each of which is then modeled by a reduced RC circuit characterized by the same set of S-Parameters (Figure 1)

- This permits the analysis of interconnect models other than RC-trees, and therefore, coupling capacitors and resistor loops can be handled without loss of generality

- Also, partitionning of the circuit into small multiport components leads to smaller size matrix computation, saving time and memory, while increasing accuracy

- Output of HIPEX-CRC is thus a realizable, simulable reduced network. Figure 2 depicts the HIPEX-CRC reduction flow

Key Features

- HIPEX-CRC supports SPICE, DSPF and SPEF input formats and outputs SPICE, DSPF and SPEF reduced netlists. Possibility is given to the user to output SPEF from DSPF input, as well as output DSPF starting from a SPEF output

- HIPEX-CRC is fast: SPICE netlist ranging about 1.5 million parasitic elements can be processed within some 5 minutes on a 64bit-Linux standard machine

- For enhanced reduction, HIPEX-CRC may ignore all parasitic resistances and/or capacitances lower than a user-specified threshold. Also, HIPEX-CRC may ignore coupling capacitors present in DSPF or SPEF netlists

- For selective reduction, HIPEX-CRC may ignore user specified subcircuits and/or SPF nets.

- For custom reduction, HIPEX-CRC enables the user to specify unreducible nodes, to control topology of the circuit

- Any reduction step performed by HIPEX-CRC is reported to a summary file (detailed or simple, on the user choice)

- HIPEX-CRC is easy to use, thanks to user-friendly graphical interface, and flexible LISA scripting language

- HIPEX-CRC is available for Unix, Linux32-64bit, Windows