赋能下一代高压功率器件:从仿真到系统的氧化镓沟槽肖特基二极管

β-Ga2O3 有望彻底变革高压功率转换领域,其超低损耗和高临界电场特性使之成为下一代功率器件的理想选择[1],能够为AI数据中心供电、可再生能源系统[2]、高压断路器和静电放电保护[3]提供1–6 kV、0.5–0.8 kA范围内的三相高压直流的AC/DC和DC/AC转换方案。

β-Ga2O3 有望彻底变革高压功率转换领域,其超低损耗和高临界电场特性使之成为下一代功率器件的理想选择[1],能够为AI数据中心供电、可再生能源系统[2]、高压断路器和静电放电保护[3]提供1–6 kV、0.5–0.8 kA范围内的三相高压直流的AC/DC和DC/AC转换方案。

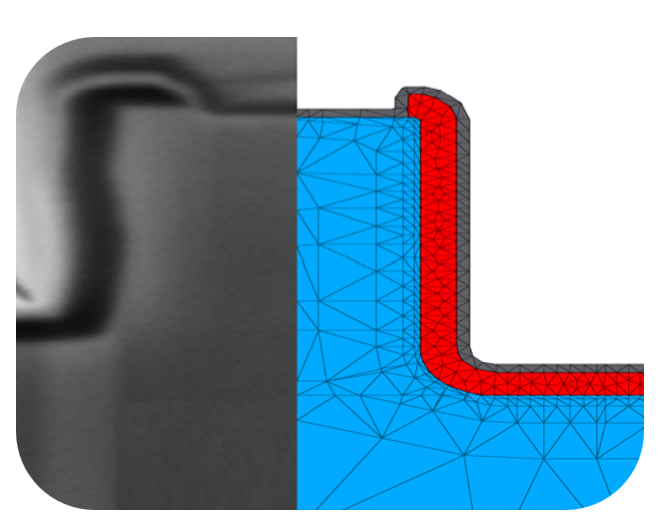

由于材料固有特性阻碍了实际空穴导电性[4],实现p型β-Ga₂O₃面临挑战,这限制了广泛用于功率和逻辑器件中电流整流的p-n结的形成。在缺乏p-n同质结的情况下,β-Ga₂O₃二极管最初必须依赖肖特基结架构[5]。近年来,采用场板结构的横向β-Ga₂O₃肖特基势垒二极管已展现出令人瞩目的击穿电压(>10 kV)[8]。然而,垂直器件架构因其通过调整外延层厚度即可扩展至更高电流和电压,同时节省芯片面积的固有优势而更受青睐[9]。此外,为缓解肖特基接触处的高电场,降低因热电子场发射[6]、镜像力势垒降低[6]以及等离子体刻蚀引起的陷阱辅助隧穿[7]可能导致的反向泄漏电流,在β-Ga₂O₃基肖特基势垒二极管中应用了降低表面电场技术。这促使β-Ga₂O₃垂直沟槽肖特基势垒二极管成为优选器件架构——其中用于形成肖特基接触的鳍状结构被沟槽隔开,通过在鳍壁侧形成基于Al₂O₃的垂直金属-氧化物-半导体结来实现降低表面电场效应。此类二极管的失效主要受介质击穿而非金属-半导体结控制。虽然Al₂O₃可承受约8.7 MV/cm的电场[10],但沟槽角处的电场集中会导致该区域介质层中的电场超过临界值。因此,在反向偏压下,介质中的高电场可能引发灾难性失效,而更厚的介质层虽更稳固,却可能削弱鳍结构中的降低表面电场效果[9]。在早期开发阶段建立仿真模型以研究器件几何结构对其承载能力的影响,并构建用于基于SPICE的电路仿真的紧凑模型至关重要。

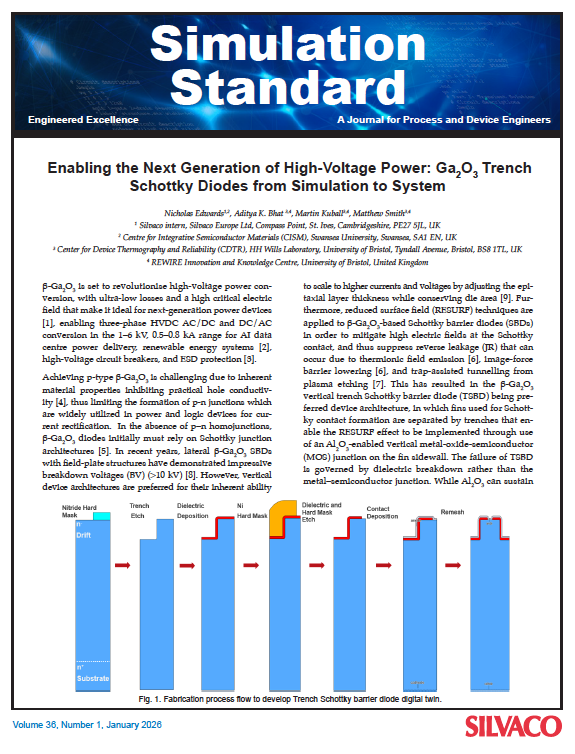

本仿真报告展示了一个β-Ga₂O₃垂直沟槽肖特基势垒二极管从基于实验数据的TCAD建模,到紧凑模型提取,再到SPICE级电路分析的全过程。β-Ga₂O₃垂直沟槽肖特基势垒二极管在布里斯托大学洁净室及表征实验室完成制备与电学测试,工艺仿真通过Victory Process、Victory Mesh、Victory Device工具实现,SPICE建模则采用Utmost4、Gateway和SmartSpice工具完成。