SmartSpice Does It Smart

According to the Merriam-Webster dictionary, two of the definitions for ‘smart’ are

- operating by automation and

- using a built-in microprocessor for automatic operation, for processing of data, or for achieving greater versatility

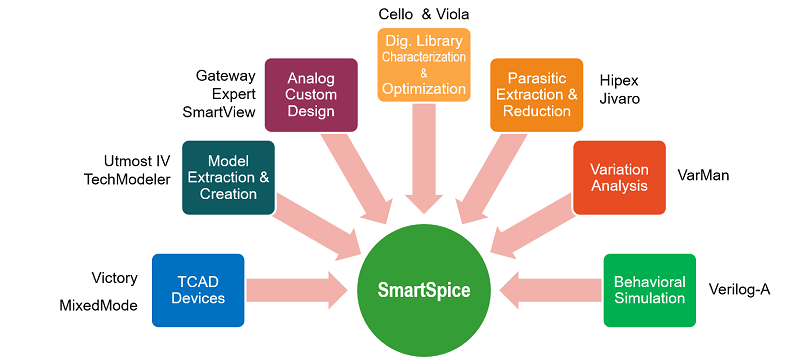

By this definition, any SPICE simulator qualifies as a smart design tool, but what about versatility? SmartSpice has had over 30 years of product development and is the Swiss Army knife of circuit simulators, with wide applicability to different CAD design flows.

SmartSpice is a versatile analysis tool used in many CAD flows.

Analog Custom Design

In a traditional analog custom design, a schematic capture tool is used to define circuit and perform an idealized simulation where the wiring is perfect and noise free. Silvaco Gateway schematic tool launches SmartSpice with the circuit netlist derived from the entered schematic and launches the SmartView waveform viewer to visualize the results. SmartView can plot results as they are being generated by a running SmartSpice simulation for instant feedback on the analysis. Design improvement is supported in two ways. The Rubberband feature of Gateway and SmartSpice allows for exploration of the circuit by changing component values, e.g. Rs and Cs, to see what effect they have on a target specification of interest, e.g. bandwidth versus gain. SmartSpice has a built-in multi-target optimizer that will tune device values to achieve the desired goals. The optimized values have to be back-annotated to the design schematic manually.

Post-layout Simulation Flow

When a design schematic is committed to a physical layout, a post-layout circuit analysis can be performed. The Expert layout editor from Silvaco is ideal for launching these kinds of simulations. It is integrated with RC parasitic extraction tools, such as Hipex and Stellar, that use 2.5D and 3D solvers to determine the R and C values from the layout. The simulation file generated by Expert brings together the combined circuitry with the parasitic of the wiring. One caveat of post-layout simulation is that the presence of RC parasitics one needs to pay the price in simulation speed in order to have the benefits of higher accuracy. Typically, there are 10X greater number of elements to simulate versus an unannotated netlist. Fortunately, RC reduction technology can reduce the number of parasitics to improve simulation speed without sacrificing accuracy. Silvaco’s RC reduction tool Jivaro is a comprehensive reduction system that provides selective control of what paths are reduced and how aggressive is the applied reduction. Jivaro can be invoked from SmartSpice. By the correct application of Jivaro, post-layout simulation can speedup 10X to 100X. For post-layout circuit optimization for timing, power and other metrics, this faster simulation time is essential to achieve circuit improvement in a reasonable time.

Post-layout simulation flow

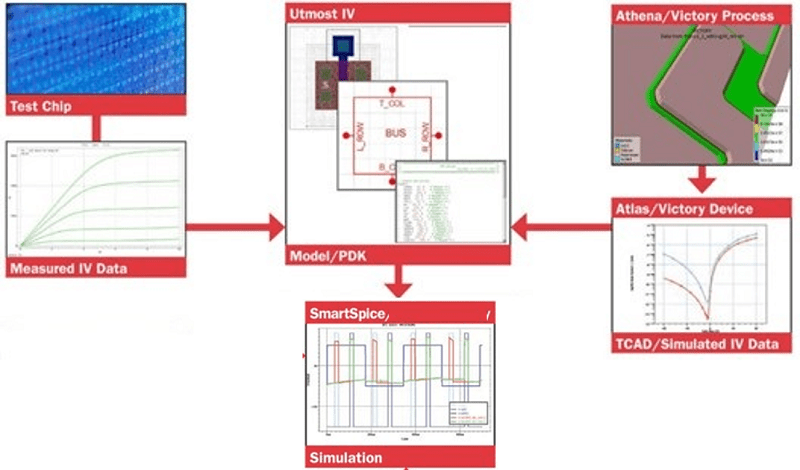

SPICE Models and the TCAD Flow

SPICE simulation device models (diodes, MOSFETs, BJTs, etc.) require parameters to match the behavior of actual devices. For circuit designers, device parameters are typically defined in the Process Development Kit (PDK) for a foundry. The process of generating the model parameters requires I/V curve data to be fed to a model generation tool, like Silvaco Utmost IV. Silvaco has been offering SPICE modeling services and software since its inception in the 1980’s and is very experienced in producing accurate models. The necessary I/V curve data can be obtained either by measurements of a test chip/device or by using a virtual fab simulation using Silvaco Victory Process and VIctory Device TCAD software. It should be noted that poor modeling can lead to simulation problems, such as non-convergence, which halt analysis. To mitigate simulation problems, Utmost IV runs SmartSpice to validate that the model will work properly in SPICE circuit simulation.

SmartSpice modeling flow

Behavioral Modeling

What if I have a non-standard device to simulate? Silvaco TechModeler can create a custom behavioral model, in Verilog-A format, using I/V curve data, which can be run in SmartSpice.. Verilog-A format is an Industry standard sharing mechanism for behavioral models. It can be used for behavioral block design or compact model design. V-A code is much more portable than C code, but it runs at a slower speed. If writing your own Verilog-A model, SmartSpice provides a V-A debugger environment to ensure the numerical properties of a model (e.g. the derivatives) are correct and that any discontinuities or convergence issues are fixed. SmartSpice also has a built-in Verilog-A-to-C compiler, which is able to pre-compile Verilog-A code for the first simulation and reuse it for future runs of the same circuit. This provides the user with both Verilog-A portability and C-like performance.

Cell Characterization

Cell characterization is usually done in an automated (batch) flow for generating timing and other models for digital synthesis tools, typically in the Liberty file format including setup and hold times, power profiles, etc. The Silvaco tool, Viola, is one example of an automated characterization system. To perform all the required Process/Voltage/Temperature corner analyses for a given cell library, Viola launches hundreds of SmartSpice simulations to achieve accurate cell models. For smaller scale characterization efforts, particularly for unique custom cells, SmartSpice has its own built-in measurement capabilities and can analyze data from multiple previous simulation runs.

Variability and Yield Analysis

One important analysis for standard cells and for memories is their variability in performance due to manufacturing and environmental effects and how this impacts the yield of correctly performing circuits. With variability analysis, designers can improve yield despite variations in manufacturing. A 1% improvement could translate into an increase of profitability of hundreds of thousands of dollars. Traditional Monte Carlo analysis is available in SmartSpice, but the number of simulation runs to achieve 3-sigma can take many hours, or even days. To achieve 3- to 6-sigma analysis of variability, billions of simulations would need to be done. Silvaco VarMan uses machine learning techniques to do a Fast Monte Carlo high-sigma analysis of circuits using SPICE simulation, such as SmartSpice. Reduction of needed simulations can be on the order of 100,000X for analysis of an SRAM bit-cell.

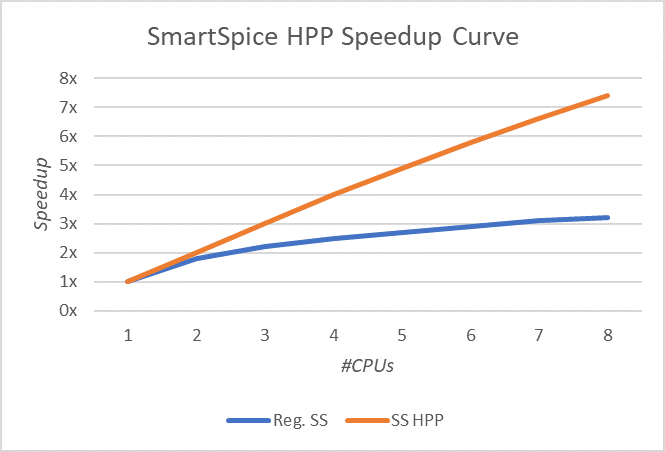

SmartSpice HPP

HPP (High Performance Parallel) is a SmartSpice simulation mode that can increase simulation speed by up to 2X even on single CPU computers. When it comes to parallelization, one can have almost linear speedup when using HPP mode. HPP takes the global circuit numerical matrix and decomposes it into subcircuits (blocks) which are calculated separately, then the final result is adjusted using the interconnection between all subcircuits. Using the recommended solver with HPP will cause each subcircuit to have its own small matrix instead of one global matrix. This reduces computation time and provides additional speedup.

SmartSpice HPP mode speedup curve when compared with regular SmartSpice.

FastSPICE

SmartSpice also provides FastSPICE simulation performance. With SmartSpice Pro, design applications such as SRAMs and TFT-based displays that use array of repeated circuitry of cells can be accelerate simulations by 10X. It incorporates SPICE traditional simulation algorithms for accuracy and uses a variety of methods to optimize the analysis including:

- Event-driven communication between active and latent partitions of the design

- Multi-rate simulation

- Exploiting linear RCL clusters in the circuit

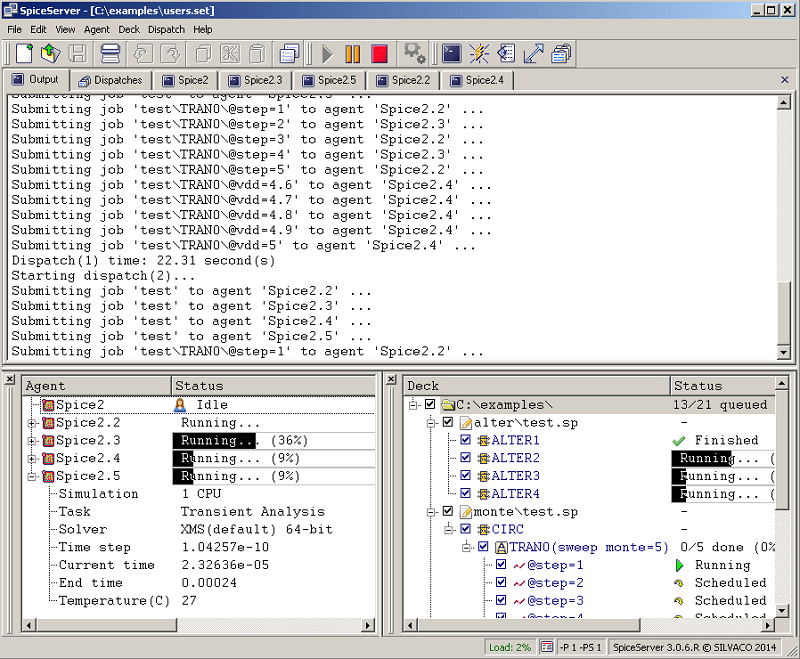

Smart SpiceServer™

SpiceServer is a Silvaco utility that allows you to simulate one or more input decks using multiple SmartSpice agents (slaves) running typically on remote hosts. The power of SpiceServer is splitting a single input deck into constituting branches (sub-decks), and simulate this deck in parallel with several agents. These simulation branches may come from the use of .ALTER, Monte Carlo and SWEEP statements, miscellaneous analyses, etc. By making use of remote agents, it becomes possible to significantly reduce a simulation time and improve overall performance over just using standalone simulator in multi-core mode. SpiceServer can operate in a convenient GUI that controls all simulation activity.

Smart SpiceServer monitoring all simulation branches (jobs) from a single input deck.

API for Embedded User Applications

The SmartSpice API is a set of functions for building embedded user applications. The API accesses the features in the parser, simulation engine, and post-processor. Some examples include:

- Circuit creation without using netlists

- Modification of accuracy, and analysis parameters

- Device/model parameters modifications

- Simulation data extraction

A user app calls functions from an IPC library to communicate with SmartSpice API core functions. Silvaco provides C-code examples as a starting point and the API contains roughly 100 functions which gives the user total control of the simulator. User applications may also use the graphical capabilities of SmartView waveform viewer via the SmartSpice API.

SmartSpice Does It

SmartSpice is a full-featured simulator with extensive model support and analysis types and provides Verilog-A for custom behavioral modeling. It has been adopted globally for over 30 years and supports a wide variety of circuit types. It offers a range of speed/capacity capabilities including FastSPICE and has tight flow integrations with

- Design entry and layout

- Spice and behavioral modeling

- Characterization

- Variability analysis

- Parasitic extraction / reduction

- Parallel, sliced and accelerated simulation

- Custom integration API interface

SmartSpice does it smart, when you need SPICE modeling and circuit simulation and analysis.