How to Accelerate Post-layout Parasitics Analysis and Avoid Wasted Simulation Cycles

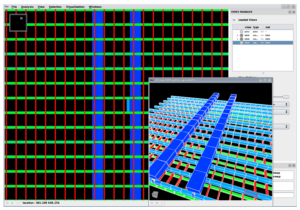

Parasitic extraction is the cornerstone of signoff verification. The exponential growth of RC parasitics in advanced technology nodes, leads to longer post-layout simulation times and unexpected results that can take days or weeks to debug and waste simulation resources. In this webinar we will introduce Silvaco’s unique parasitic analysis and debug tools that will help solve these crucial issues. We will show how these tools can be used to prevent unexpected results when parasitic extraction flows are updated. We will review solutions that help understand what is inherently going on in the post-layout design, allowing design teams to improve debugging and optimization steps and increase effectiveness of backend flow.

Parasitic extraction is the cornerstone of signoff verification. The exponential growth of RC parasitics in advanced technology nodes, leads to longer post-layout simulation times and unexpected results that can take days or weeks to debug and waste simulation resources. In this webinar we will introduce Silvaco’s unique parasitic analysis and debug tools that will help solve these crucial issues. We will show how these tools can be used to prevent unexpected results when parasitic extraction flows are updated. We will review solutions that help understand what is inherently going on in the post-layout design, allowing design teams to improve debugging and optimization steps and increase effectiveness of backend flow.

Presenter

Mr. Simon-Alexis Abric is a corporate application engineer for Silvaco. He is responsible for customer technical support for parasitic reduction and analysis tools. Mr. Abric earned a Master of Engineering degree in integrated circuits and systems in 2013 from the engineering school ENSEIRB in Bordeaux, France.

WHO SHOULD ATTEND:

- Designers looking to accelerate post-layout simulation analysis and optimize their layout

- CAD and PDK engineers looking for solutions to compare and improve parasitic extraction flows

- Engineers looking for methods to build custom analysis flows based on parasitic-centric figures (resistance, capacitance, interconnect delays)

When: April 20, 2021

Where: Online

Time: 10:00am-10:30am-(PDT)

Language: English