Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

HINTS & TIPS – September 1998

I run DRC, find one-two violations, correct them, then I re-run DRC to check whether my corrections worked. However re-running on the whole design is time-consuming. How can I run DRC over a piece of the layout, in the vicinity of the introduced changes?

Recursive Cutting of Rectangular Partitions for VLSI Floorplanning

Rectangular partitionings form a mathematical base for many modern approaches to automation of VLSI design [1-3]. In particular, popular methodologies of hierarchical placement (by cell grouping / merging) as well as procedures of global routing and layout compression deal with partitions that can be hierarchically subdivided into components of bounded complexity.

Real-time DRC in Expert Layout Editor

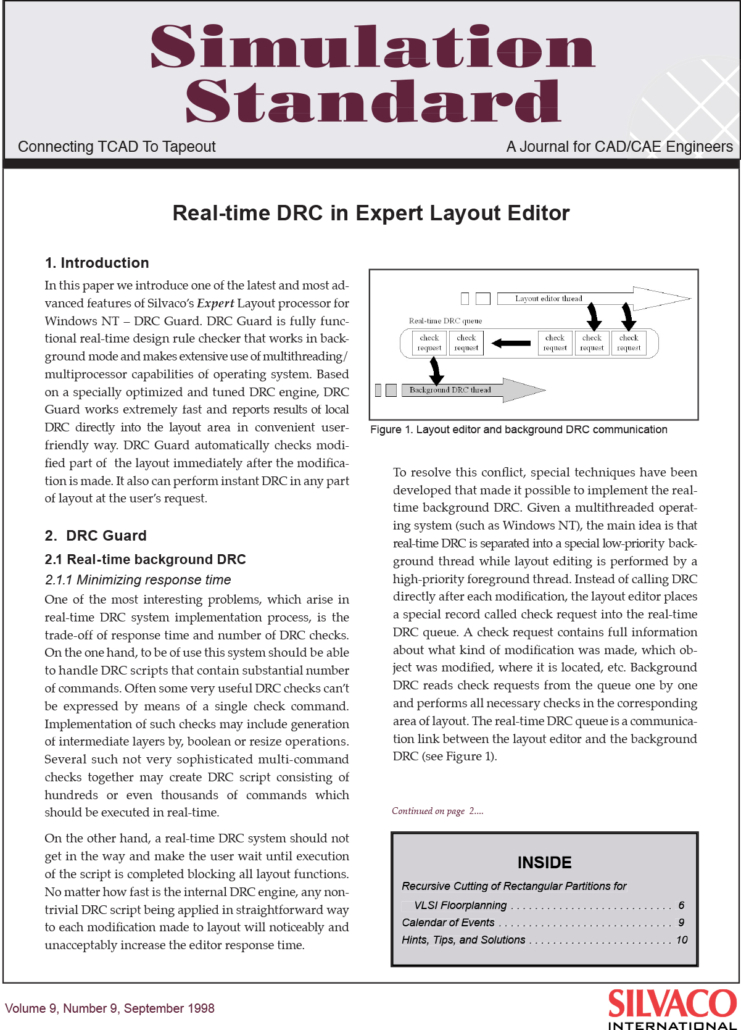

In this paper we introduce one of the latest and most advanced features of Silvaco's Expert Layout processor for Windows NT DRC Guard. DRC Guard is fully functional real-time design rule checker that works in background mode and makes extensive use of multithreading/ multiprocessor capabilities of operating system.

HINTS & TIPS – August 1998

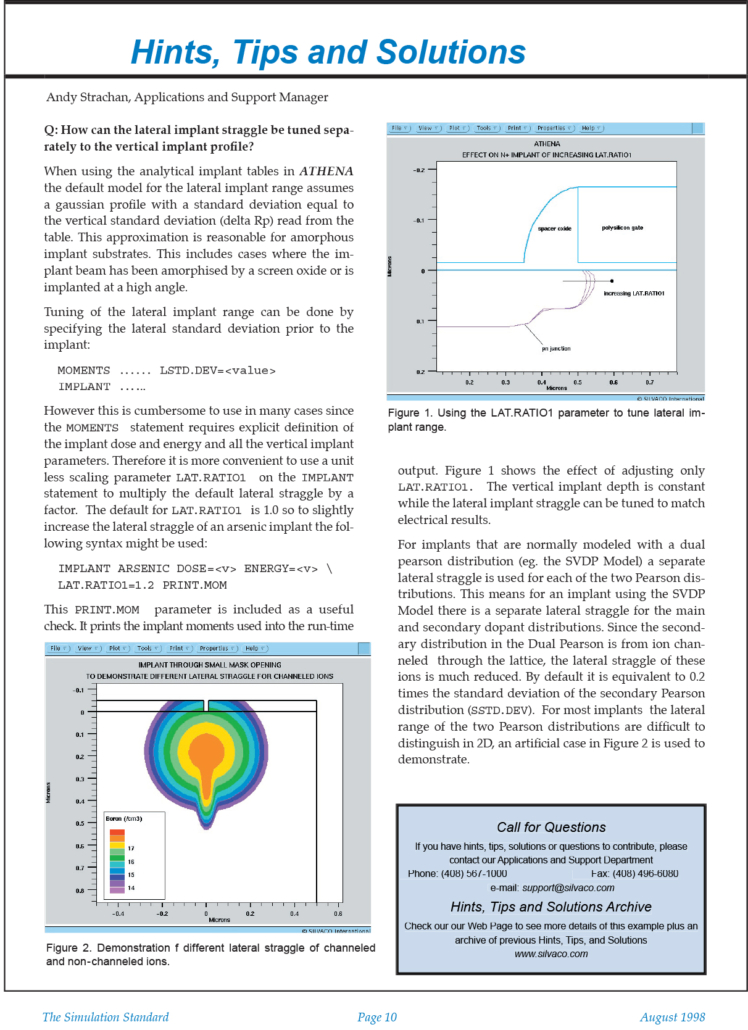

When using the analytical implant tables in ATHENA the default model for the lateral implant range assumes a gaussian profile with a standard deviation equal to the vertical standard deviation (delta Rp) read from the table. This approximation is reasonable for amorphous implant substrates.

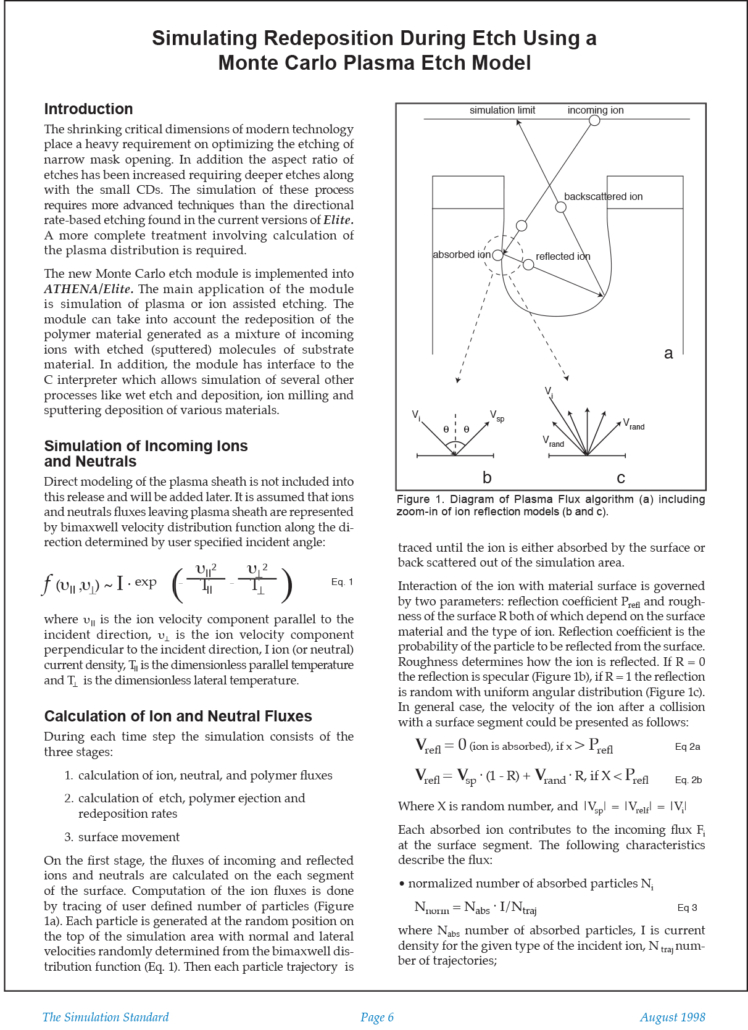

Simulating Redeposition During Etch Using a Monte Carlo Plasma Etch Model

The shrinking critical dimensions of modern technology place a heavy requirement on optimizing the etching of narrow mask opening. In addition the aspect ratio of etches has been increased requiring deeper etches along with the small CDs. The simulation of these process requires more advanced techniques than the directional rate-based etching found in the current versions of Elite. A more complete treatment involving calculation of the plasma distribution is required.

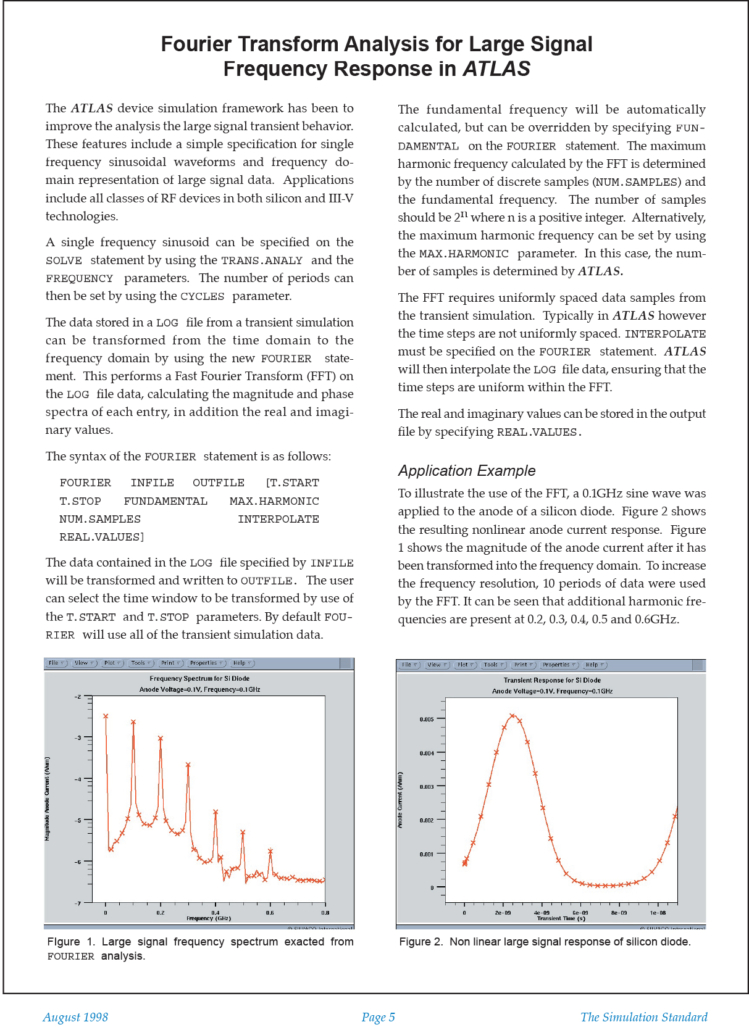

Fourier Transform Analysis for Large Signal Frequency Response in ATLAS

The ATLAS device simulation framework has been to improve the analysis the large signal transient behavior. These features include a simple specification for single frequency sinusoidal waveforms and frequency domain representation of large signal data. Applications include all classes of RF devices in both silicon and III-V technologies.