Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

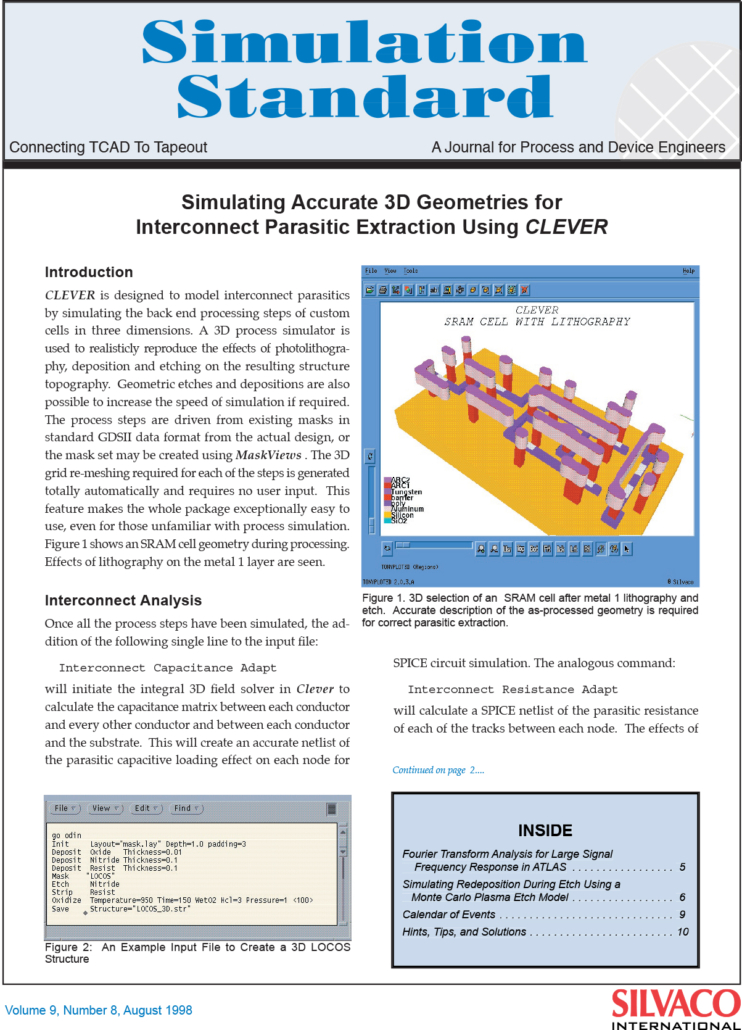

Simulating Accurate 3D Geometries for Interconnect Parasitic Extraction Using CLEVER

CLEVER is designed to model interconnect parasitics by simulating the back end processing steps of custom cells in three dimensions. A 3D process simulator is used to realisticly reproduce the effects of photolithography, deposition and etching on the resulting structure topography

HINTS & TIPS – July 1998

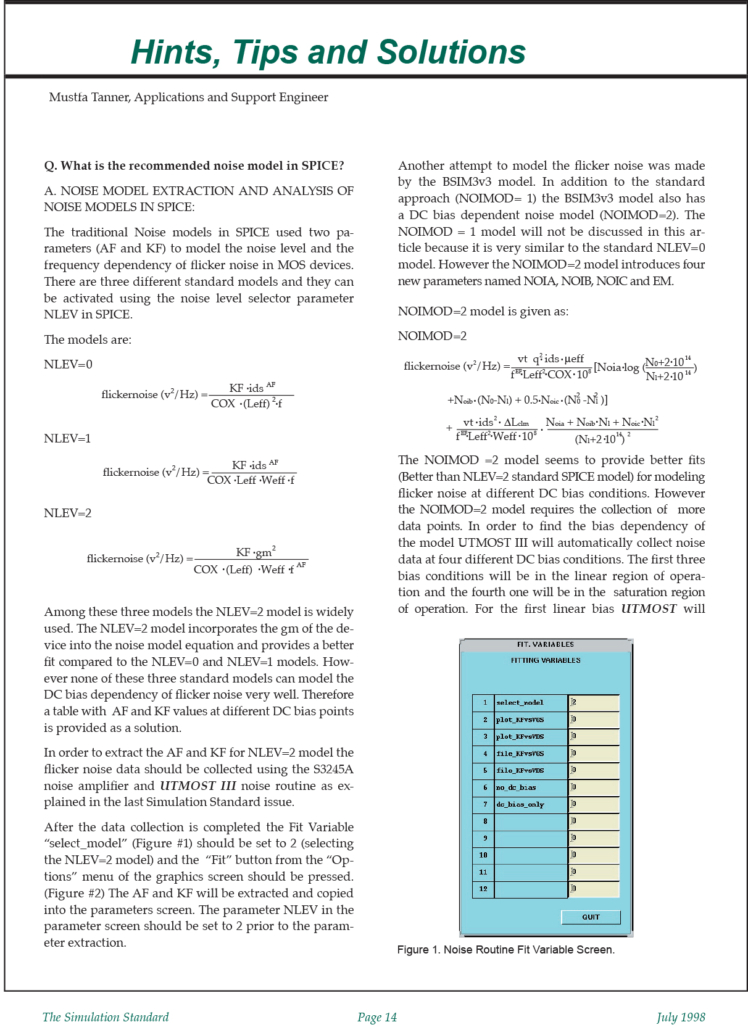

The traditional Noise models in SPICE used two parameters (AF and KF) to model the noise level and the frequency dependency of flicker noise in MOS devices. There are three different standard models and they can be activated using the noise level selector parameter NLEV in SPICE.

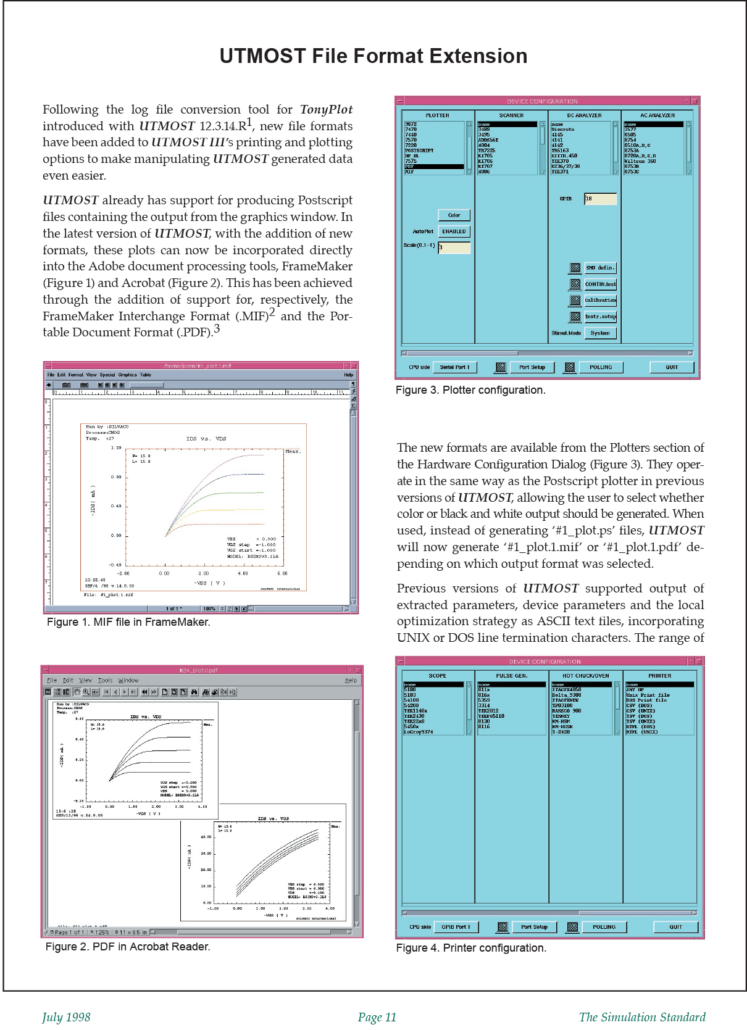

UTMOST File Format Extension

Following the log file conversion tool for TonyPlot introduced with UTMOST 12.3.14.R1, new file formats have been added to UTMOST III's printing and plotting options to make manipulating UTMOST generated data even easier.

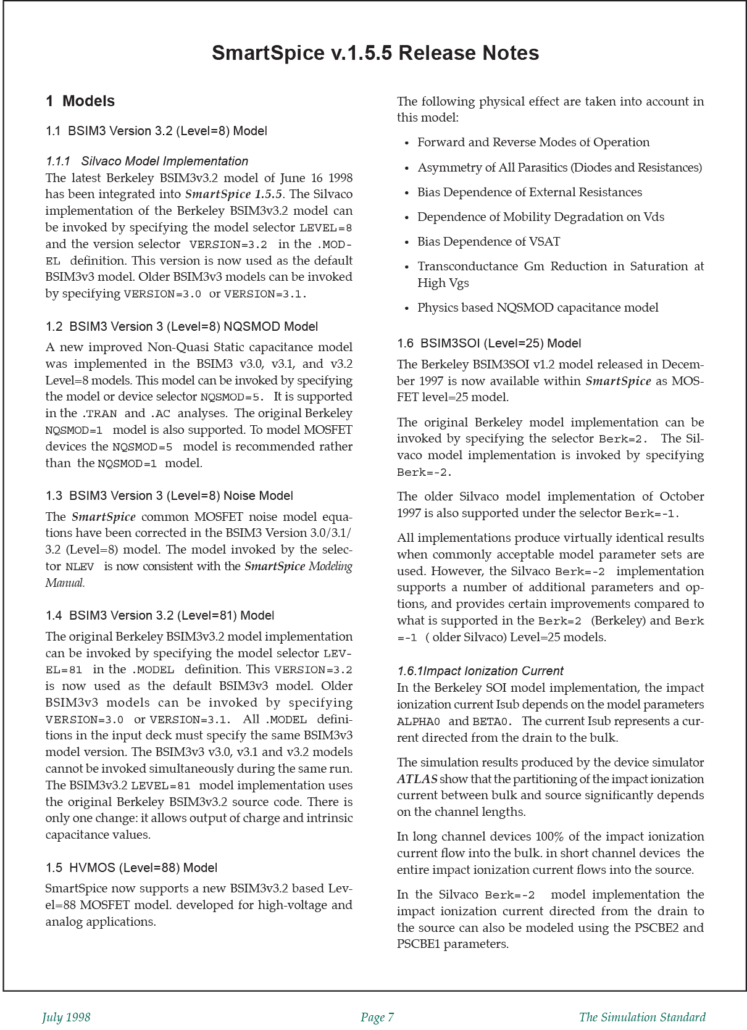

SmartSpice v.1.5.5 Release Notes

The latest Berkeley BSIM3v3.2 model of June 16 1998 has been integrated into SmartSpice 1.5.5. The Silvaco implementation of the Berkeley BSIM3v3.2 model can be invoked by specifying the model selector LEVEL=8 and the version selector VERSION=3.2 in the .MODEL definition. This version is now used as the default BSIM3v3 model. Older BSIM3v3 models can be invoked by specifying VERSION=3.0 or VERSION=3.1.

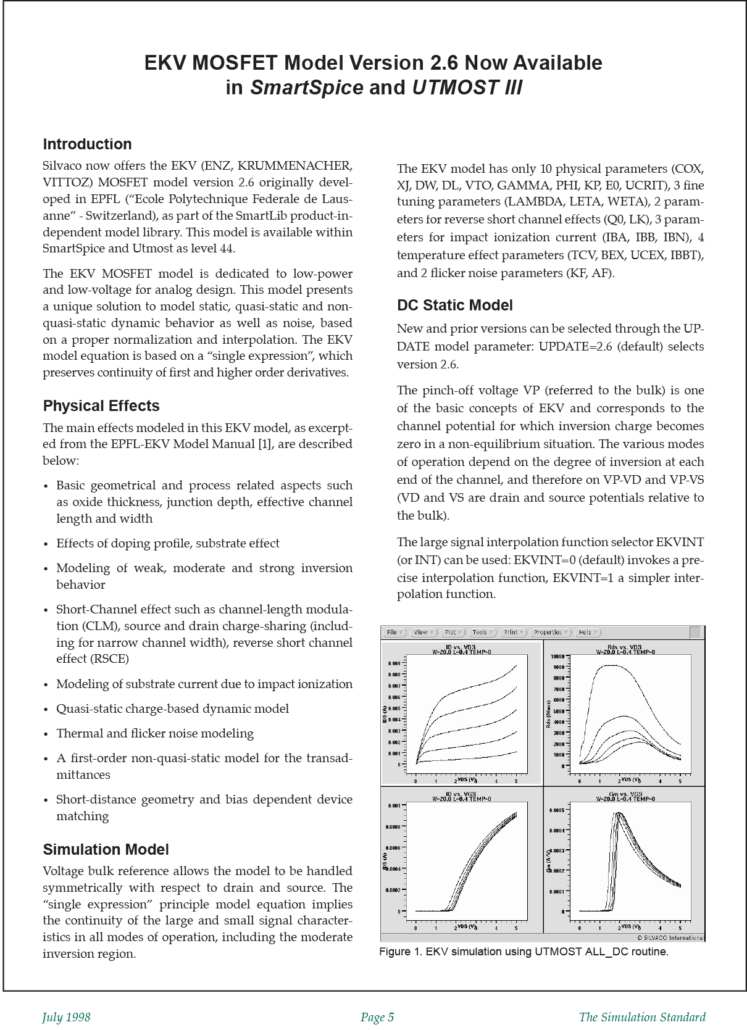

EKV MOSFET Model Version 2.6 Now Available in SmartSpice and UTMOST III

Silvaco now offers the EKV (ENZ, KRUMMENACHER, VITTOZ) MOSFET model version 2.6 originally developed in EPFL ("Ecole Polytechnique Federale de Lausanne" - Switzerland), as part of the SmartLib product-independent model library. This model is available within SmartSpice and UTMOST as level 44.

BSIM3v3.2 Model Released in SmartSpice and UTMOST III

The latest Berkeley BSIM3v3.2 model of June 16 1998 is now available in the SmartSpice 1.5.5 release.

Two BSIM3v3.2 implementations are supported in SmartSpice and UTMOST III.