Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

Hints & Tips July 1999

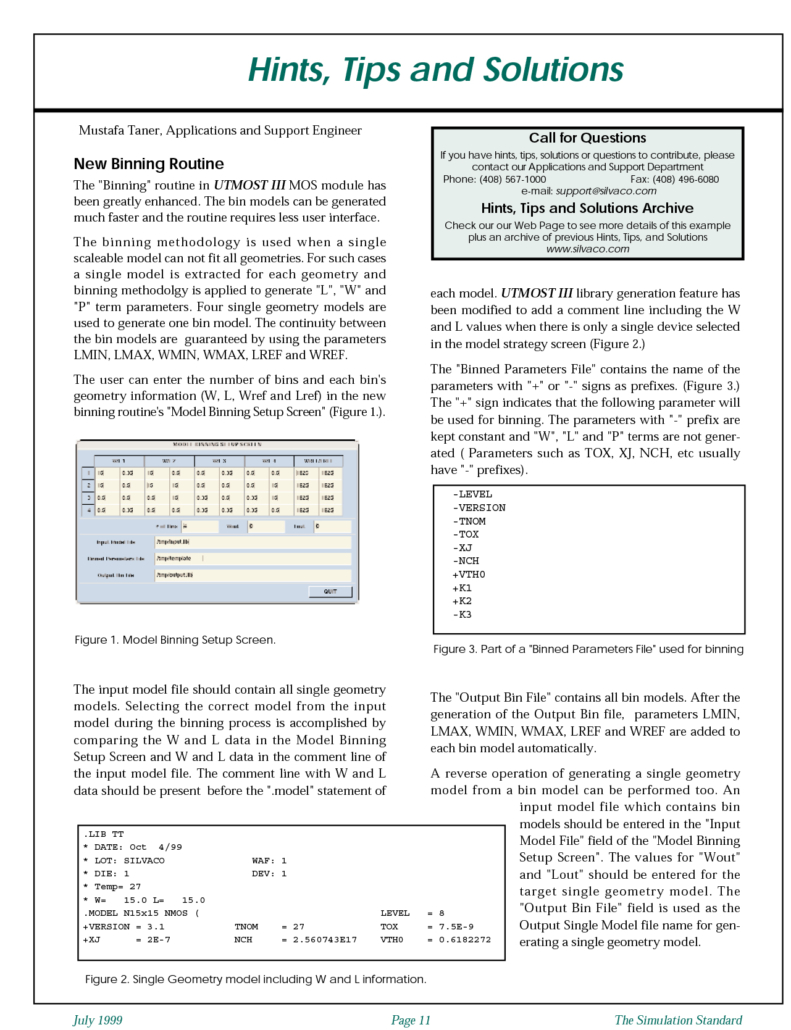

The "Binning" routine in UTMOST III MOS module has been greatly enhanced. The bin models can be generated much faster and the routine requires less user interface.

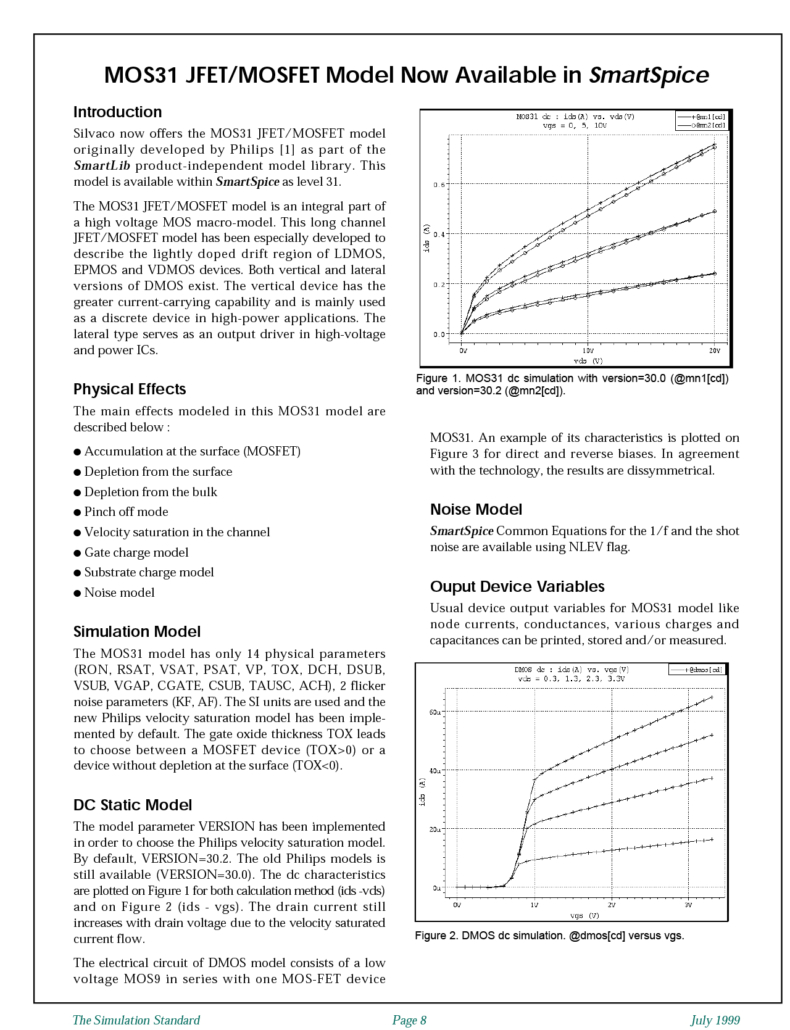

MOS31 JFET/MOSFET Model Now Available in SmartSpice

Silvaco now offers the MOS31 JFET/MOSFET model originally developed by Philips [1] as part of the SmartLib product-independent model library. This model is available within SmartSpice as level 31.

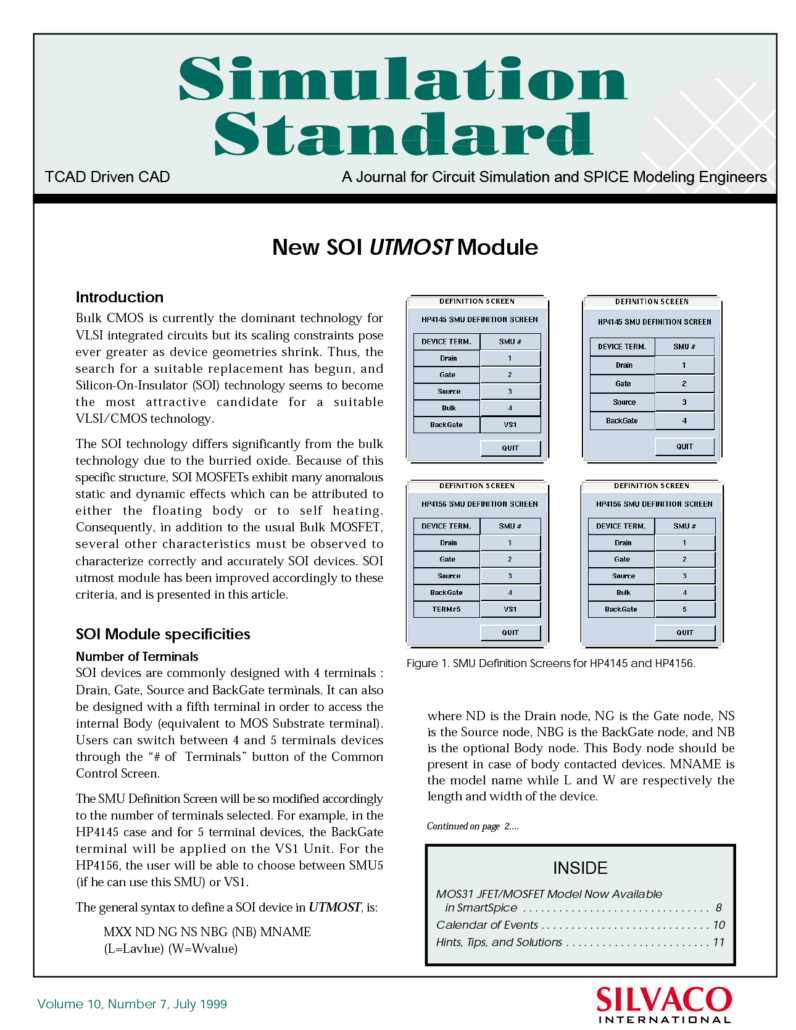

New SOI UTMOST Module

Bulk CMOS is currently the dominant technology for VLSI integrated circuits but its scaling constraints pose ever greater as device geometries shrink. Thus, the search for a suitable replacement has begun, and Silicon-On-Insulator (SOI) technology seems to become the most attractive candidate for a suitable VLSI/CMOS technology.

Hints & Tips May 1999

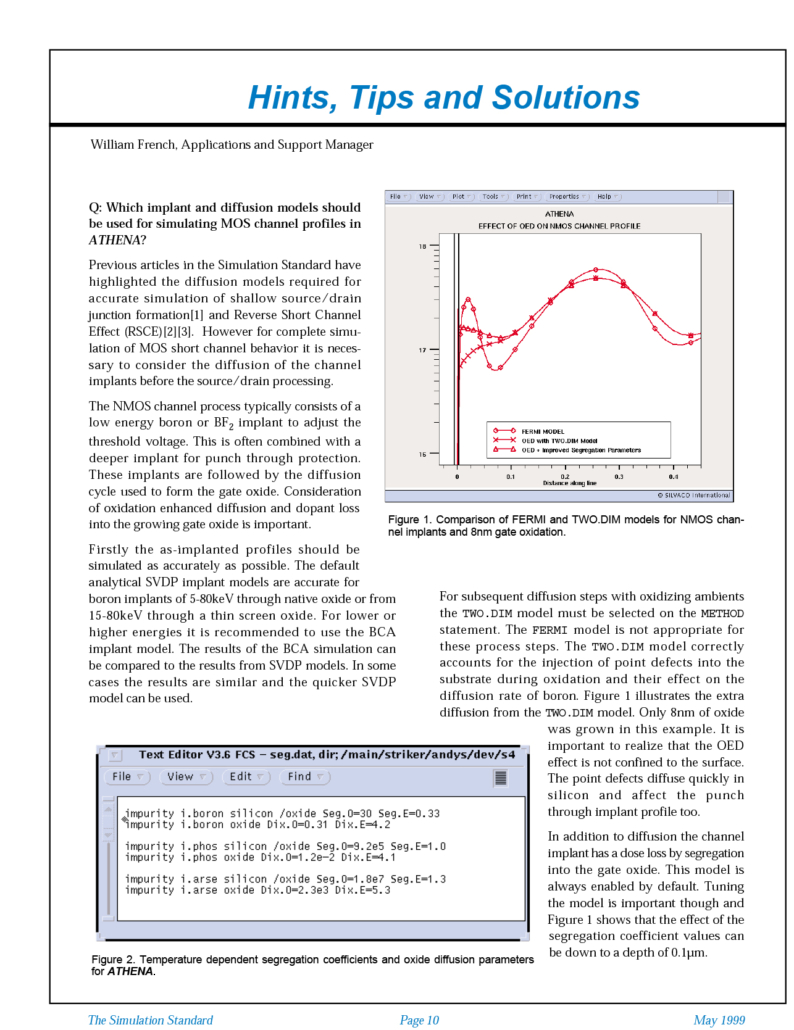

A. Previous articles in the Simulation Standard have highlighted the diffusion models required for accurate simulation of shallow source/drain junction formation[1] and Reverse Short Channel Effect (RSCE)[2][3]. However for complete simulation of MOS short channel behavior it is necessary to consider the diffusion of the channel implants before the source/drain processing.

Hints & Tips June 1999

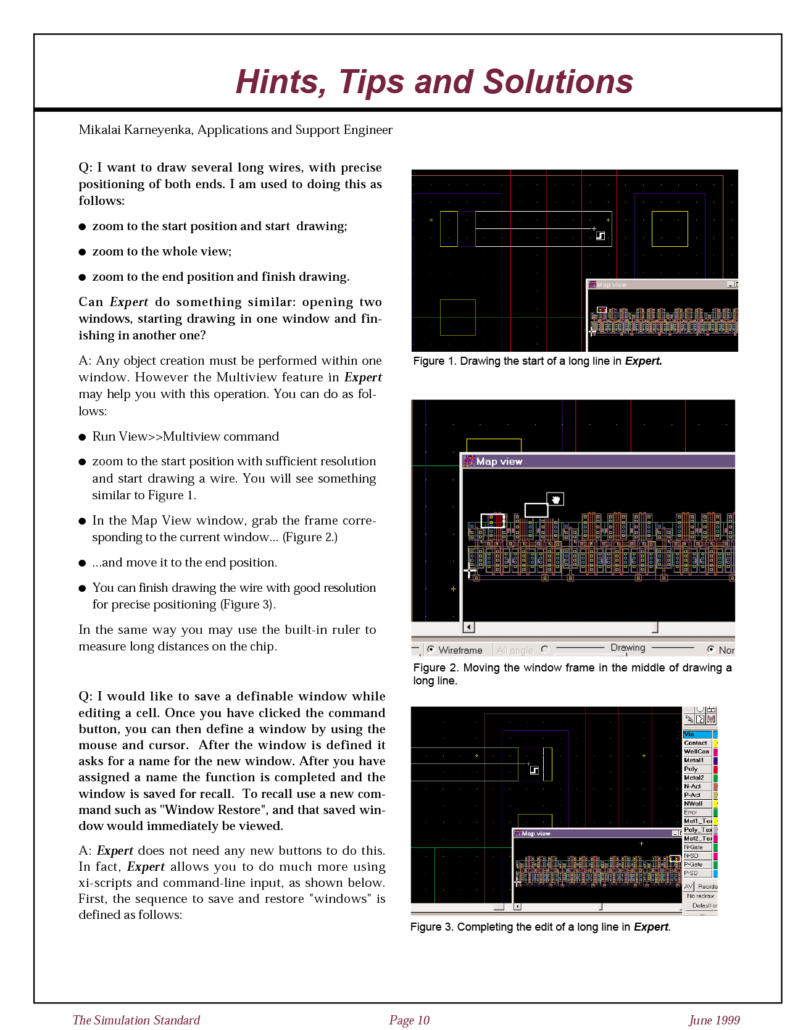

Q: I want to draw several long wires, with precise positioning of both ends. I am used to doing this as follows:

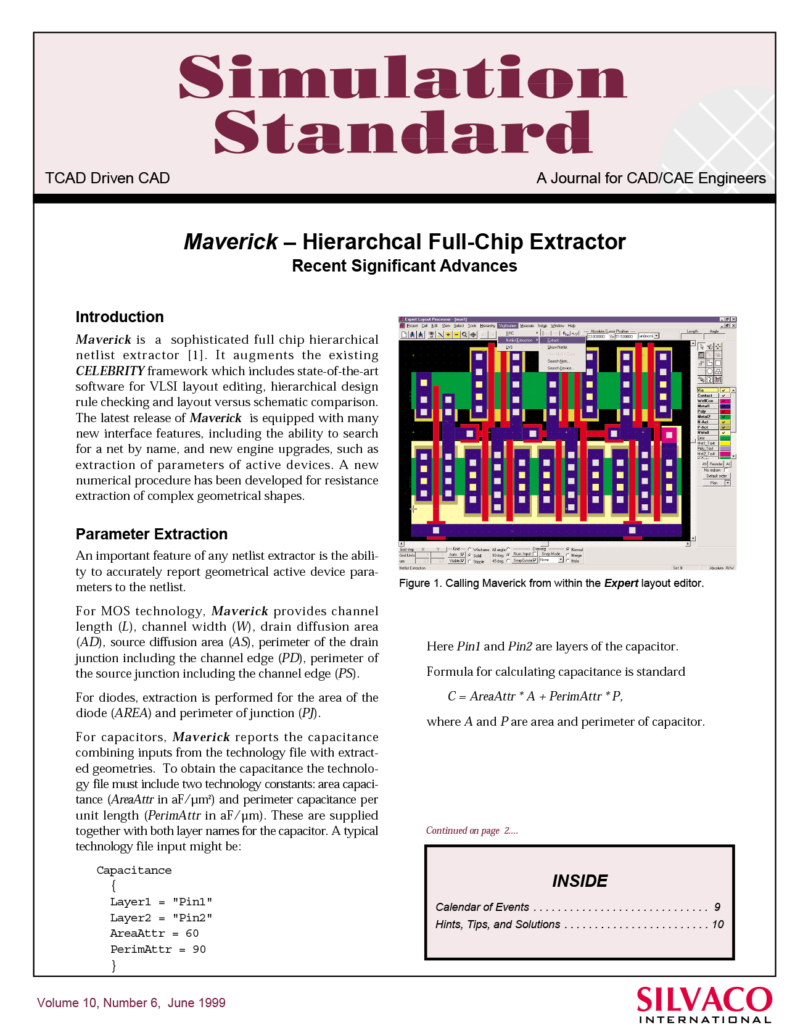

Maverick- Hierarchcal Full-Chip Extractor Recent Significant Advances

Maverick is a sophisticated full chip hierarchical netlist extractor [1]. It augments the existing CELEBRITY framework which includes state-of-the-art software for VLSI layout editing, hierarchical design rule checking and layout versus schematic comparison. The latest release of Maverick is equipped with many new interface features, including the ability to search for a net by name, and new engine upgrades, such as extraction of parameters of active devices. A new numerical procedure has been developed for resistance extraction of complex geometrical shapes.