Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

“Shortest Path” Option for Flight Line Style (Net Bar)

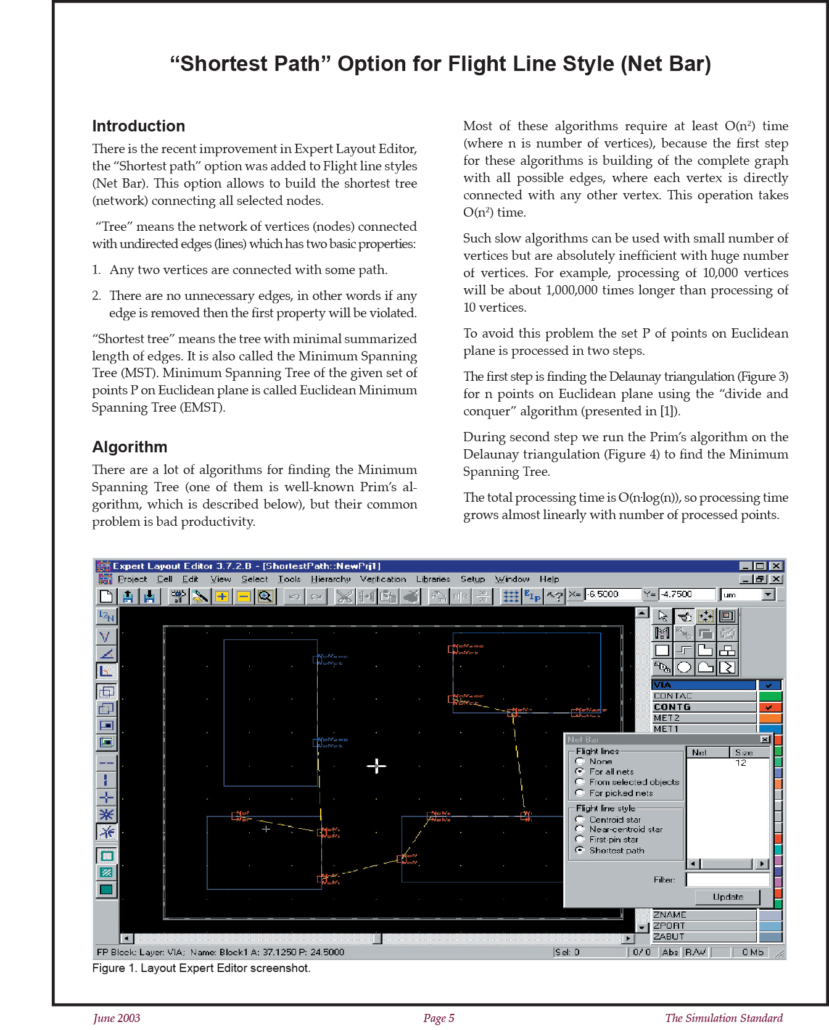

There is the recent improvement in Expert Layout Editor, the “Shortest path” option was added to Flight line styles (Net Bar). This option allows to build the shortest tree (network) connecting all selected nodes.

Expert Layout Editor Recent Improvements: Over-the-Point Drawing of Orthogonal Shapes

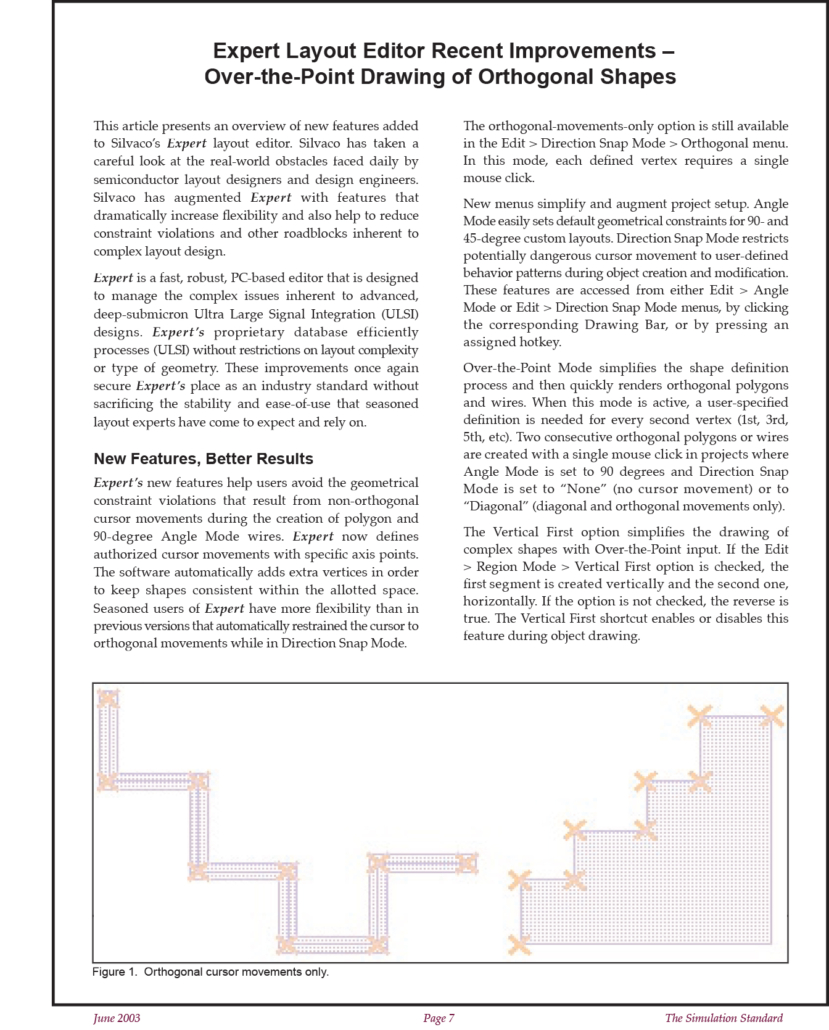

This article presents an overview of new features added to Silvaco's Expert layout editor. Silvaco has taken a careful look at the real-world obstacles faced daily by semiconductor layout designers and design engineers. Silvaco has augmented Expert with features that dramatically increase flexibility and also help to reduce constraint violations and other roadblocks inherent to complex layout design.

Guardian DRC Edge Layer Operations

Recent versions of Guardian DRC introduce operations that involve edge layers, either on input or on output. An edge layer is a layer that contains line segments that are edges or parts of edges of shapes from other layers. These edges have "inner" and "outer" surfaces defined according to the shape layers they were derived from.

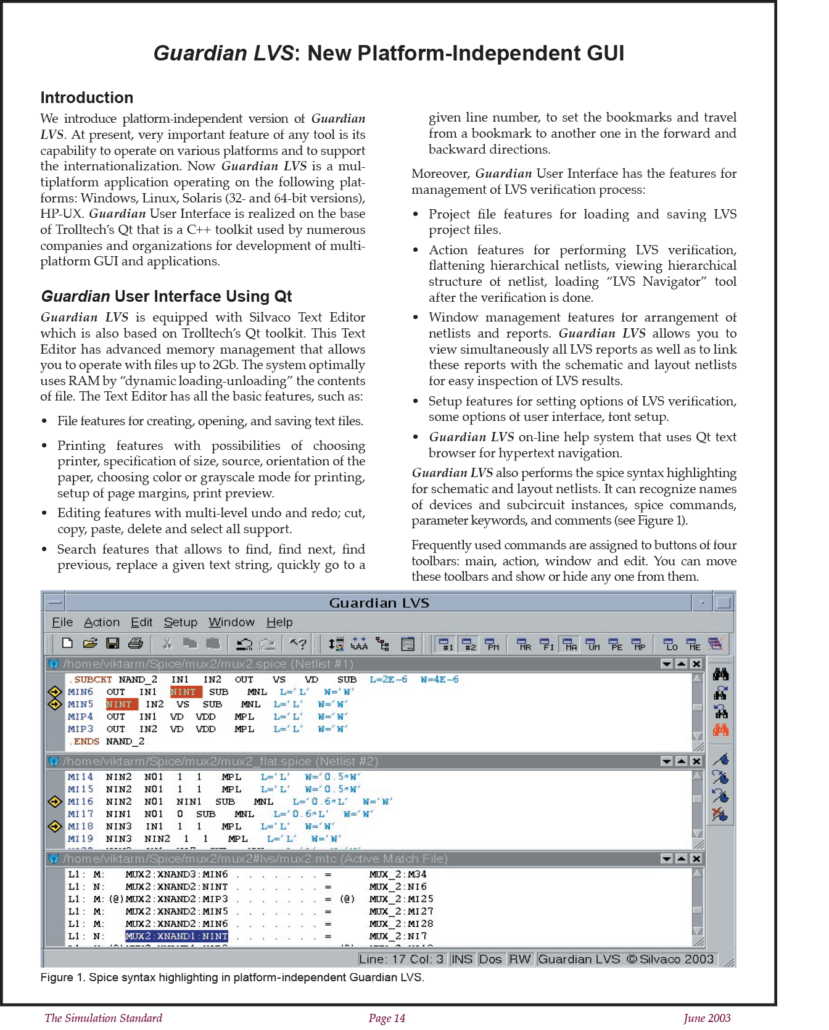

Guardian LVS: New Platform-Independent GUI

We introduce a platform-independent version of Guardian LVS. An important feature of any tool is its capability to operate on various platforms and to support internationalization. Now Guardian LVS is a multiplatform application operating on the following platforms: Windows, Linux and Solaris (32- and 64-bit versions).

Counting Instances in an Expert Editor Layout

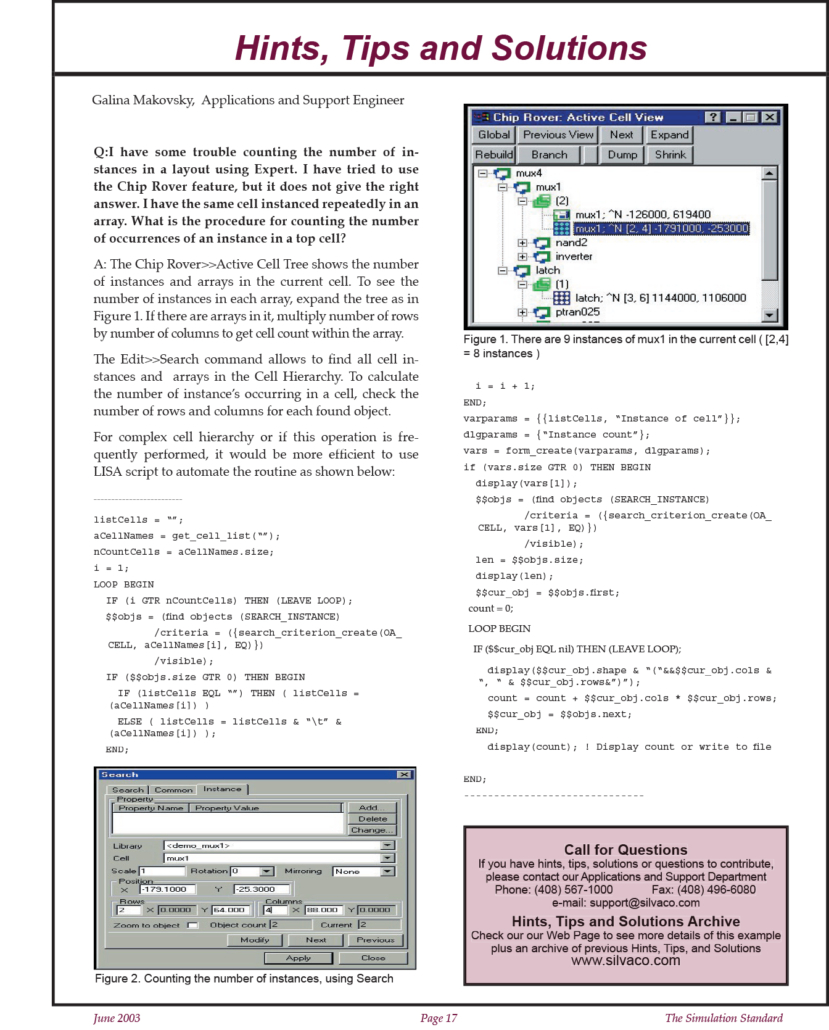

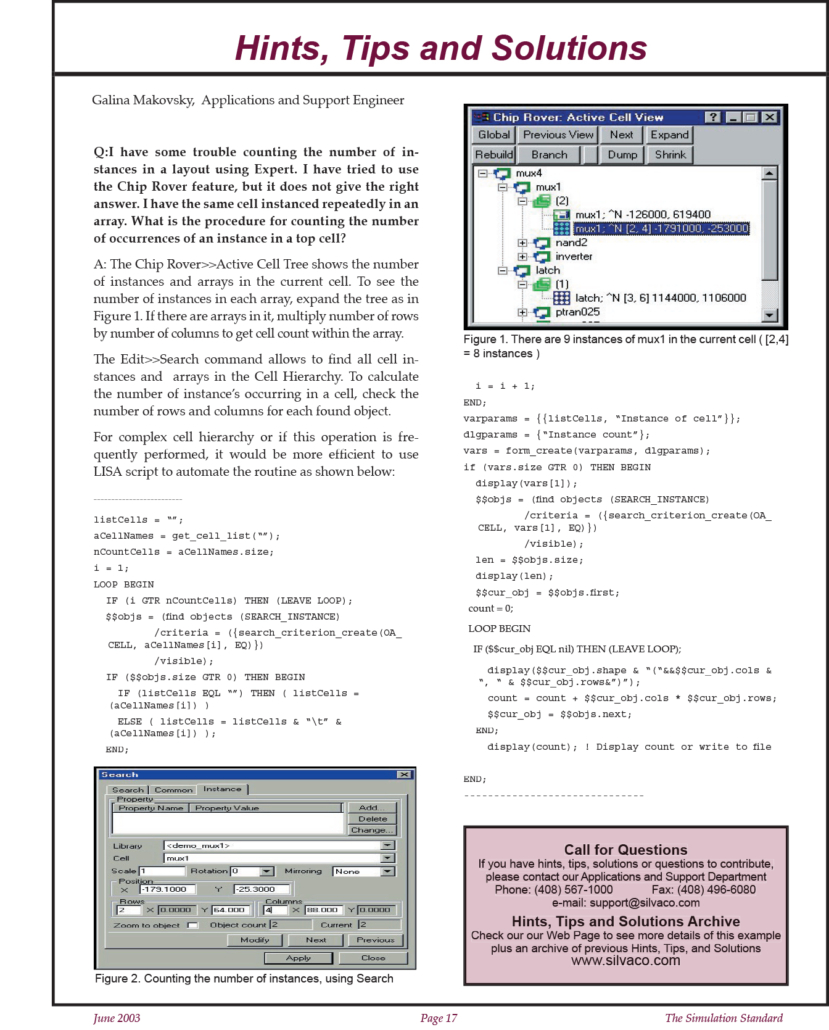

Q: I have some trouble counting the number of in-stances in a layout using Expert. I have tried to use the Chip Rover feature

Low Voltage Super Junction MOSFET Simulation and Experimentation

The application of Super Junction concepts to a low voltage power MOSFET is investigated. The body junction is modified with the addition of a high energy implant, resulting in an increased breakdown voltage. Simulations are used to quantify the relationship between dose and breakdown voltage, resulting in a predicted 35% Rds(on) reduction. This is confirmed through experiment, and a 19% reduction in Rds(on) is reported at 75 V. No change in device reliability is observed. This approach provides a simple means to reduce the on resistance of low voltage MOSFETs.