HINTS & TIPS – April 1998

Q. What is the typical method of measuring flicker noise using S3245A Noise Amplifier?

SPICE Model Validation

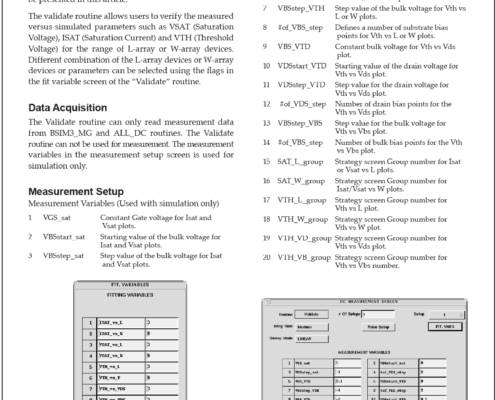

The importance of the MOS device SPICE model validation and the introduction of the validation routine in UTMOST III was presented in Simulation Standard article issued on September 1996. The recent developments and the practical applications for the "Validate" routine will be presented in this article.

UTMOST Log File Conversion for TonyPlot

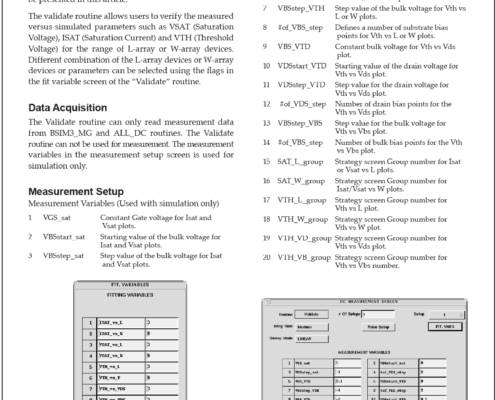

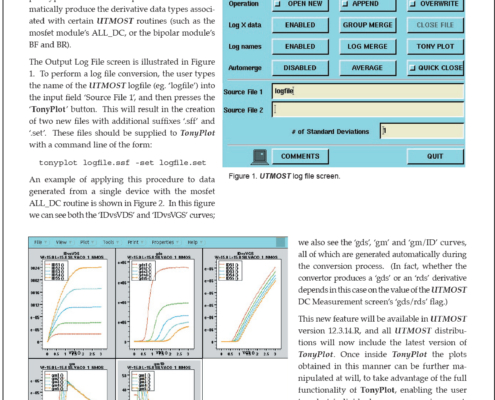

A new feature has recently been added to UTMOST: the ability to convert UTMOST log files into a format suitable for viewing in TonyPlot. This new feature is controlled from the UTMOST Output Log File screen, and is compatible with all UTMOST plot types. The conversion process will also automatically produce the derivative data types associated with certain UTMOST routines (such as the mosfet module's ALL_DC, or the bipolar module's BF and BR).

Advanced Cell Characterization Using SmartSpice Scripting Features

In a previous article [1], the efficient use of the SmartSpice .MODIF statement for cell characterization was discussed. This article will focus on using advanced features of the SmartSpice scripting language to solve this problem in a more flexible manner.

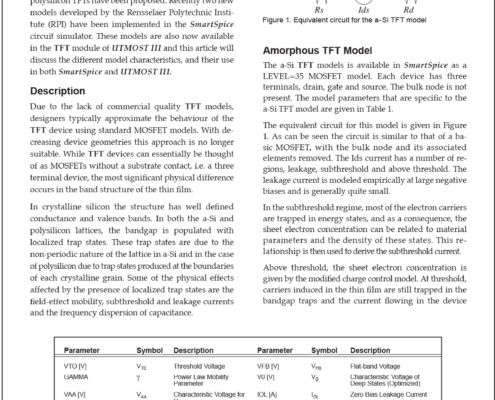

Release of RPI Amorphous Silicon and Polysilicon TFT Models in SmartSpice and UTMOST

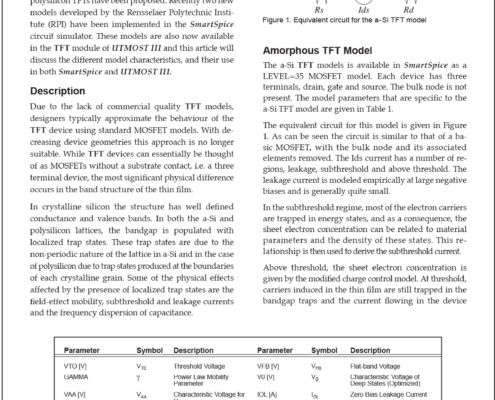

Thin film transistors (TFTs) have an important application in the manufacture of active matrix LCD displays. As this technology has become more mature, a number of different models of both amorphous silicon (a-Si) and polysilicon TFTs have been proposed. Recently two new models developed by the Rensselaer Polytechnic Institute (RPI) have been implemented in the SmartSpice circuit simulator. These models are also now available in the TFT module of UTMOST III and this article will discuss the different model characteristics, and their use in both SmartSpice and UTMOST III.

Release of an Upgraded SmartSpice Interface to Cadence

The SmartSpice Interface to Cadence integrates the Analog Artist and Composer elements of the Cadence Design Framework II (DFII) with SmartSpice. This integration is accomplished, in versions 4.4.0 and later of DFII, through the Cadence Spice Socket (cdsSpice) and the OASIS interface in the Analog Artist and Composer components of DFII. Versions of DFII prior to 4.4.0 are also supported by SmartSpice, but these solutions rely on the older HSPICE Socket, and necessarily offer substantially less functionality than is provided by the current interface.

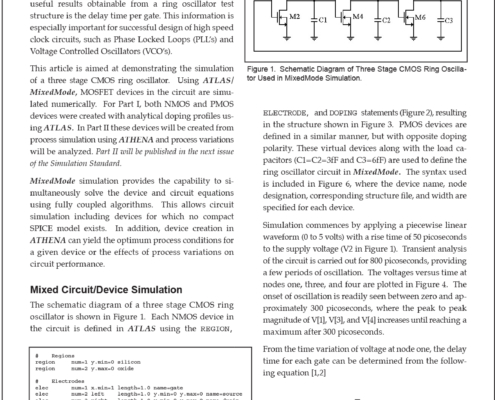

ATLAS/MixedMode Simulation of a Three Stage CMOS Ring Oscillator Part I: MixedMode Setup

Ring oscillator circuits are a valuable test structure for determining the feasibility and success of an integrated circuit process fabrication sequence. One of the most useful results obtainable from a ring oscillator test structure is the delay time per gate.

BSIM3SOI Level=25 Model Released in SmartSpice

The Berkeley BSIM3SOI model, released in December 1997, is now available within SmartSpice as the MOSFET level=25 model. This model incorporates three separate implementations: the original Berkeley model implementation is invoked with the selector Berk=2; the Silvaco implementation is invoked with Berk=-2.

Scanbox Approach to Shape Reconstruction for Automated Reticle Inspection

The paper describes a generalization of the scanline approach [1] to reconstruction of the shape of planar object represented by a discrete point set with a given distance threshold d. This problem arises in applications of VLSI layout image processing, e.g., during automated reticle inspection.

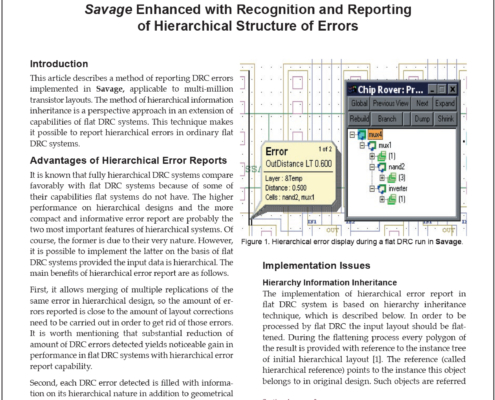

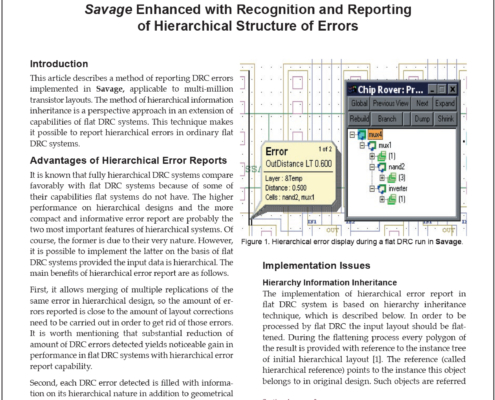

Savage Enhanced with Recognition and Reporting of Hierarchical Structure of Errors

This article describes a method of reporting DRC errors implemented in Savage, applicable to multi-million transistor layouts. The method of hierarchical information inheritance is a perspective approach in an extension of capabilities of flat DRC systems. This technique makes it possible to report hierarchical errors in ordinary flat DRC systems.