A Sophisticated Verilog-A Debugger

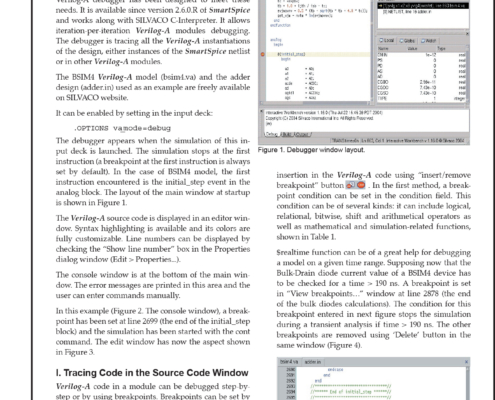

During the elaboration of a Verilog-A model, debugging a module can be very useful for detecting non-physical behavior or fine-tuning the model. The SILVACO Verilog-A debugger has been designed to meet these needs. It is available since version 2.6.0.R of SmartSpice and works along with SILVACO C-Interpreter. It allows iteration-per-iteration Verilog-A modules debugging. The debugger is tracing all the Verilog-A instantiations of the design, either instances of the SmartSpice netlist or in other Verilog-A modules.

Noise Simulations

If the MOS model file has the parameters: noia, noib, noic, Af, Kf and nlev=0 will SmartSpice ignore the BSIM III noise parameters (noia, noib and noic)

EDIF Conversion Flow on Gateway

EDIF has been a vital part of the Electronic Design Automation (EDA) industry for many years and Gateway allows users to convert edif200 formatted files of other tools vendors into Gateway’s schematics and symbols.

Hipex-CRC Parasitic RC-Network Reducer

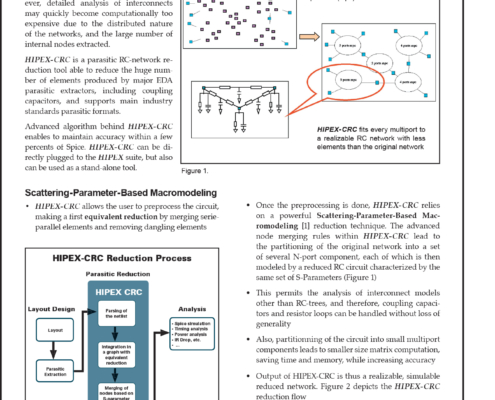

Design of large scale chips requires precise knowledge of interconnect delays. However, detailed analysis of interconnects may quickly become computationally too expensive due to the distributed nature of the networks, and the large number of internal nodes extracted.

SET Accurate Compact Model for SET-MOSFET Hybrid Circuit Simulation

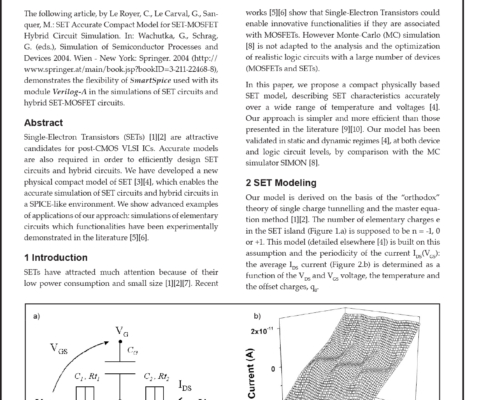

Single-Electron Transistors (SETs) [1][2] are attractive candidates for post-CMOS VLSI ICs. Accurate models are also required in order to efficiently design SET circuits and hybrid circuits

Generic Devices – The New HIPEX-NET Feature for Extraction of Custom Devices

Hipex-NET is SILVACO’s powerfull hierarchical layout netlist extractor. Built-in extracting rules permit to make fast and accurate parameter extraction for basic set of devices as MOS, BJT, diode, capacitor and resistor. But these rules can’t descibe all devices features and parameters that appeare in new submicron or RF layout designs. To resolve this problem the new HIPEX-NET command HIPEX GENERIC_DEVICE has been introduced. This new HIPEX-NET feature gives to user the capability to extract not only additional parameters for standard devices but also custom defined devices with arbitrary set of parameters. This article describes the new HIPEX-NET command.

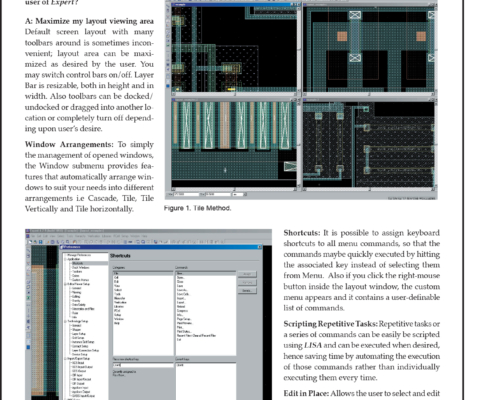

How can I become a more efficient user of Expert?

How can I become a more efficient user of Expert?

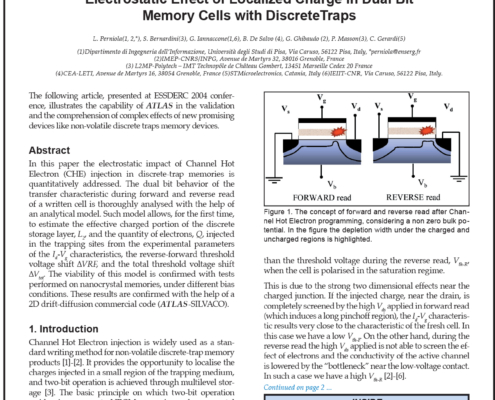

Electrostatic Effect of Localized Charge in Dual Bit Memory Cells with DiscreteTraps

In this paper the electrostatic impact of Channel Hot Electron (CHE) injection in discrete-trap memories is quantitatively addressed. The dual bit behavior of the transfer characteristic during forward and reverse read of a written cell is thoroughly analysed with the help of an analytical model. Such model allows, for the first time, to estimate the effective charged portion of the discrete storage layer, L2, and the quantity of electrons, Q, injected in the trapping

A New Efficient Quantum Method: The Bohm Quantum Potential Model

This article presents a new approach to model the quantum confinement of carriers in MOSFET or heterostructure. SILVACO has already included in its device simulator ATLAS, a Schrödinger-Poisson solver and Density-Gradient model

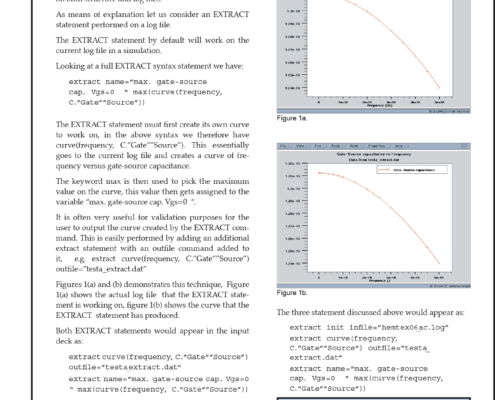

The subject of how to use the EXTRACT statement in DeckBuild often arises

The subject of how to use the EXTRACT statement in DeckBuild often arises. The EXTRACT statement is a very useful tool for analysing data and can be performed on both structure and log files.