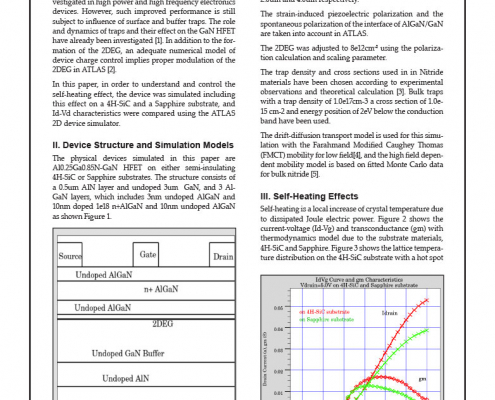

Self-Heating effect Simulation of GaN HFET Devices – 4H-SiC and Sapphire Substrate Comparison

GaN-based Hetero-Field Effect Transistors have been investigated in high power and high frequency electronics devices. However, such improved performance is still subject to influence of surface and buffer traps. The role and dynamics of traps and their effect on the GaN HFET have already been investigated [1]. In addition to the formation of the 2DEG, an adequate numerical model of device charge control implies proper modulation of the 2DEG in ATLAS [2].

Modeling of GaInP/GaAs DualJunction Solar Cells Including Tunnel Junction

This paper presents research efforts conducted at the IESUPM in the development of an accurate, physically-based solar cell model using the general-purpose ATLAS device simulator by Silvaco. Unlike solar cell models based on a combination of discrete electrical components, this novel model extracts the electrical characteristics of a solar cell based on virtual fabrication of its physical structure, allowing for direct manipulation of materials, dimensions, and dopings. As single junction solar cells simulation was yet achieved, the next step towards advanced simulations of multi-junction cells (MJC) is the simulation of the tunnel diodes, which interconnect the subcells in a monolithic MJC. The first results simulating a Dual-Junction (DJ) GaInP/GaAs solar cells are shown in this paper including a complete Tunnel Junction (TJ) model and the resonant cavity effect occurring in the bottom cell. Simulation and experimental results were compared in order to test the accuracy of the models employed.

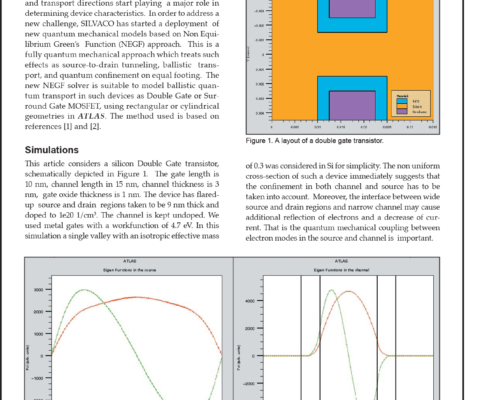

Ballistic Quantum Transport in Nanoscale Transistors: a Non Equilibrium Green’s Function Approach

Introduction

As MOS field-effect transistors are scaled down to a nanometer regime, quantum effects in both transverse and transport directions start playing a major role in determining device characteristics. In order to address a new challenge, SILVACO has started a deployment of new quantum mechanical models based on Non Equilibrium Green’s Function (NEGF) approach. This is a fully quantum mechanical approach which treats such effects as source-to-drain tunneling, ballistic transport, and quantum confinement on equal footing. The new NEGF solver is suitable to model ballistic quantum transport in such devices as Double Gate or Surround Gate MOSFET, using rectangular or cylindrical geometries in ATLAS. The method used is based on references [1] and [2].

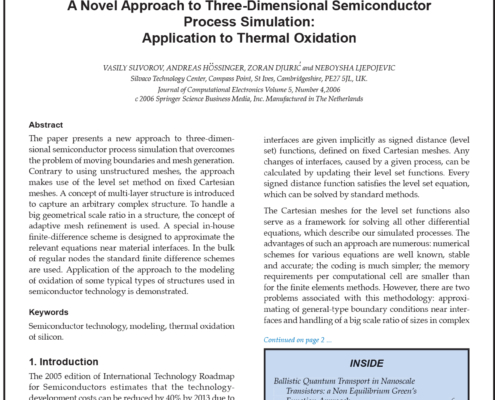

A Novel Approach to Three-Dimensional Semiconductor Process Simulation: Application to Thermal Oxidation

Abstract

The paper presents a new approach to three-dimensional semiconductor process simulation that overcomes the problem of moving boundaries and mesh generation. Contrary to using unstructured meshes, the approach makes use of the level set method on fixed Cartesian meshes. A concept of multi-layer structure is introduced to capture an arbitrary complex structure. To handle a big geometrical scale ratio in a structure, the concept of adaptive mesh refinement is used. A special in-house finite-difference scheme is designed to approximate the relevant equations near material interfaces. In the bulk of regular nodes the standard finite difference schemes are used. Application of the approach to the modeling of oxidation of some typical types of structures used in semiconductor technology is demonstrated.

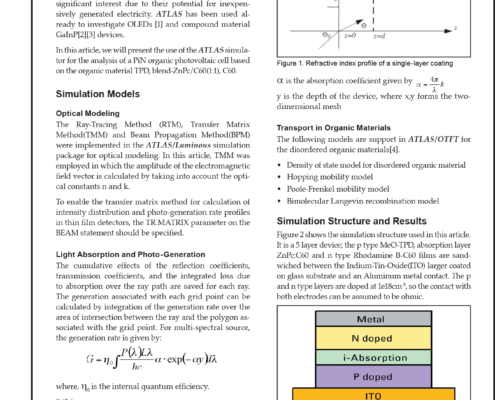

Simulation of an Organic Photovoltaic Cell (OPC) Using Atlas

Introduction

In recent years, the investigation of Organic Light Emitting Diodes (OLEDs) and photovoltaic devices based on small organic molecules and polymers has attracted significant interest due to their potential for inexpensively generated electricity. ATLAS has been used already to investigate OLEDs [1] and compound material GaInP[2][3] devices.

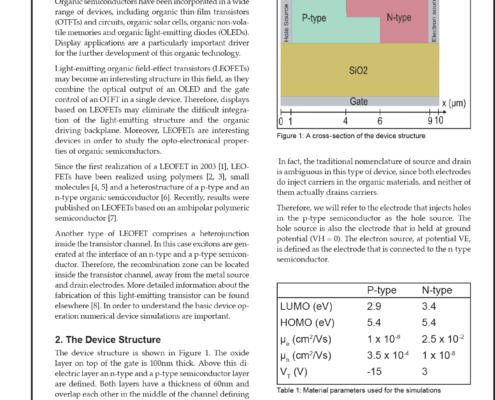

Two-Dimensional Atlas Device Simulation of an Organic Light-Emitting Field-Effect Transistor Using a Heterostructure Inside the Transistor Channel

1. Introduction

Organic semiconductors have been incorporated in a wide range of devices, including organic thin-film transistors (OTFTs) and circuits, organic solar cells, organic non-volatile memories and organic light-emitting diodes (OLEDs). Display applications are a particularly important driver for the further development of this organic technology.

Electrical Stress Degradation of Small-Grain Polysilicon Thin-Film Transistors

Abstract

This paper is focused on the stability of n-channel laser-crystallized polysilicon thin-film transistors (TFTs) submitted to a hydrogenation process during the fabrication and with small grains dimension. With the aid of numerical simulations, we investigate the effects of static stress using two types of procedures: the on stress and the hot carrier stress. Results show that the variations of trap state density into the whole polysilicon layer and not only near the drain junction are responsible for the degradation of TFTs performances in both the two types of stress and that the interface trap states play a negligible role compared to the bulk trap states.

Trapping Effects in the Transient Response of AlGaN/GaN HEMT Devices

In this paper, the transient analysis of an AlGaN/GaN high-electron mobility transistor (HEMT) device is presented. Drain–current dispersion effects are investigated when gate or drain voltages are pulsed. Gate-lag and drain-lag turn-on measurements are analyzed, revealing clear mechanisms of current collapse and related dispersion effects. Numerical 2-D transient simulations considering surface traps effects in a physical HEMT model have also been carried out.

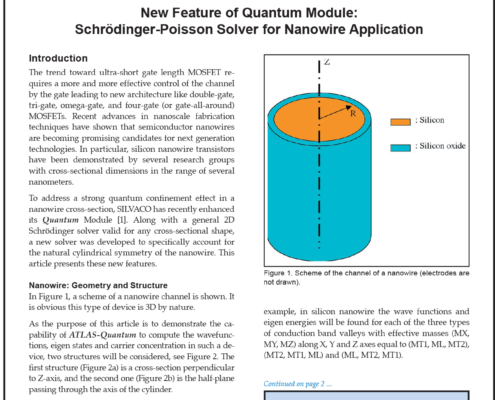

New Feature of Quantum Module: Schrödinger-Poisson Solver for Nanowire Application

Introduction

The trend toward ultra-short gate length MOSFET requires a more and more effective control of the channel by the gate leading to new architecture like double-gate, tri-gate, omega-gate, and four-gate (or gate-all-around) MOSFETs. Recent advances in nanoscale fabrication techniques have shown that semiconductor nanowires are becoming promising candidates for next generation technologies. In particular, silicon nanowire transistors have been demonstrated by several research groups with cross-sectional dimensions in the range of several nanometers.

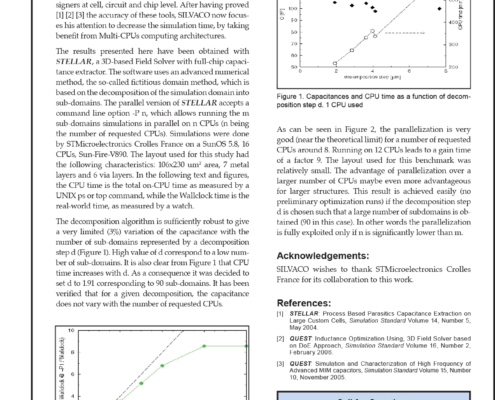

How Can I significantly Reduce Circuit Parasitics Netlist Extraction Time?

How Can I significantly Reduce Circuit Parasitics Netlist Extraction Time?