Advanced Pairwise Merging Algorithm for VLSI Floorplanning

This paper concerns the problem of determining optimal placement of rectangular blocks within a rectangular area known as the packing or cutting-stock problem. This problem arises at then floorplanning stage of VLSI design.

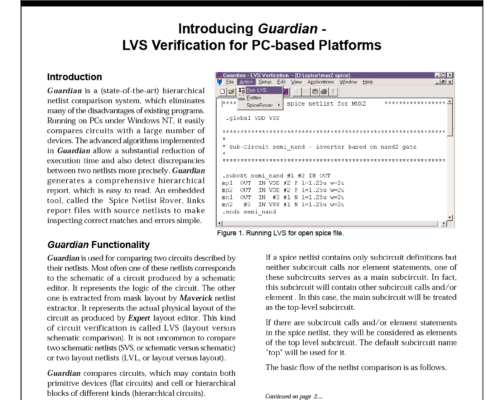

Introducing Guardian – LVS Verification for PC-based Platforms

Guardian is a (state-of-the-art) hierarchical netlist comparison system, which eliminates many of the disadvantages of existing programs. Running on PCs under Windows NT, it easily compares circuits with a large number of devices. The advanced algorithms implemented in Guardian allow a substantial reduction of execution time and also detect discrepancies between two netlists more precisely. Guardian generates a comprehensive hierarchical report, which is easy to read. An embedded tool, called the Spice Netlist Rover, links report files with source netlists to make inspecting correct matches and errors simple.

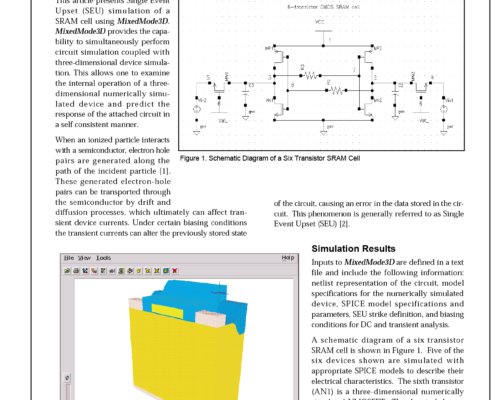

Mixed Circuit Device Simulation of Single Event Upset in a Memory Cell

This article presents Single Event Upset (SEU) simulation of a SRAM cell using MixedMode3D. MixedMode3D provides the capability to simultaneously perform circuit simulation coupled with three-dimensional device simulation. This allows one to examine the internal operation of a three-dimensional numerically simulated device and predict the response of the attached circuit in a self consistent manner.

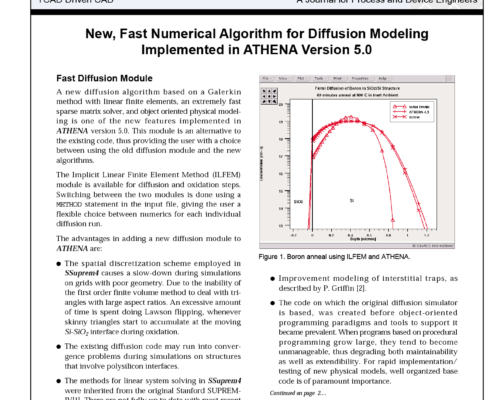

New, Fast Numerical Algorithm for Diffusion Modeling Implemented in ATHENA Version 5.0

A new diffusion algorithm based on a Galerkin method with linear finite elements, an extremely fast sparse matrix solver, and object oriented physical modeling is one of the new features implemented in ATHENA version 5.0. This module is an alternative to the existing code, thus providing the user with a choice between using the old diffusion module and the new algorithms.

Hints & Tips January 1999

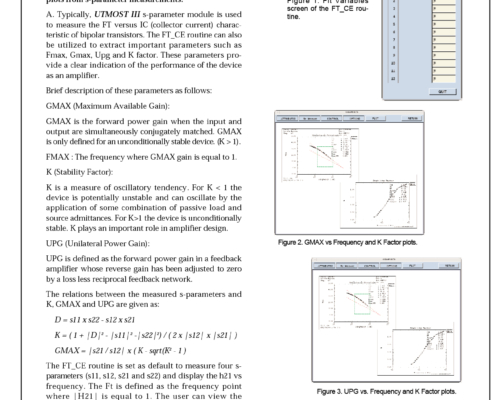

A. Typically, UTMOST III s-parameter module is used to measure the FT versus IC (collector current) characteristic of bipolar transistors. The FT_CE routine can also be utilized to extract important parameters such as Fmax, Gmax, Upg and K factor. These parameters provide a clear indication of the performance of the device as an amplifier.

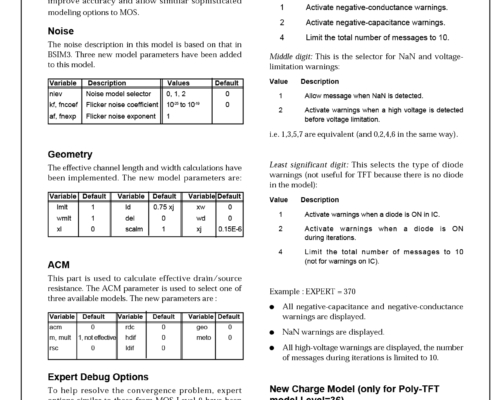

New Parameters for TFT model: Amorphous (Level=35) and Poly-Silicon (Level=36) TFT

Several enhancements have been made to the TFT models in SmartSpice. New parameters have been added to improve accuracy and allow simular sophisticated modeling options to MOS.

Enhanced Statistical Features in SPAYN Version 1.7.2

When performing statistical analyses it is often necessary to compute transformations of the observed data. This transformation may only involve a single parameter, or it may be a complicated function of several different variables. SPAYN has a new feature for generating user-defined parameters as functions of existing variables and/or constants.

New Built-in Dichotomic Search Algorithm in Smartspice

General purpose dichotomic search method is often requested by designers when they want to find a specific element (voltage, current, parameter value ...) in an already sorted set. For example, a typical problem that makes extensive use of this kind of algorithm is the computation of setup and hold time for cell characterization. This problem was already discussed in two articles [1] and [2] and a solution was proposed with the use of the SmartSpice Script Language and .MODIF statement.

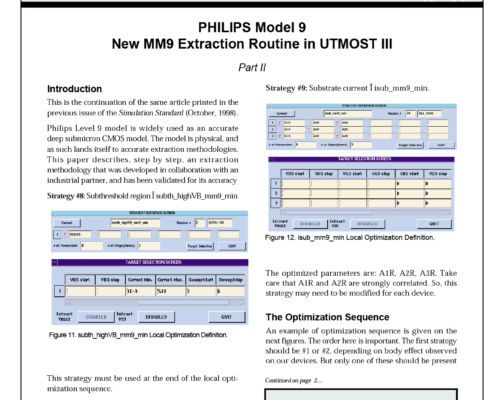

PHILIPS Model 9 New MM9 Extraction Routine in UTMOST III

Philips Level 9 model is widely used as an accurate deep submicron CMOS model. The model is physical, and as such lands itself to accurate extraction methodologies.

HINTS & TIPS – December 1998

Q: I took the example file mux4.gds from Expert's installation and tried the Edit-in-place operation. I entered into an instance of mux1, modified a box in it and exited from EIP. There are options to change the edited cell and to save instance under another cell name.