Victory TCAD 솔루션을 통해 FinFET 및 메모리 애플리케이션에서 정확한 실험 식각 프로파일을 효율적으로 달성

공정 시뮬레이션으로 복잡한 소자 구조를 만들 때, TCAD 엔지니어는 종종 반도체 제조 과정에서 이루어진 식각 프로파일을 정확하게 재현할 필요가 있습니다. 실바코 Victory Process는 몇 가지 기하학적 모델을 제공하여, 현미경 이미지 (예: 투과 전자 현미경)와 정확하게 일치하는 식각 구조를 효율적으로 달성합니다.

공정 시뮬레이션으로 복잡한 소자 구조를 만들 때, TCAD 엔지니어는 종종 반도체 제조 과정에서 이루어진 식각 프로파일을 정확하게 재현할 필요가 있습니다. 실바코 Victory Process는 몇 가지 기하학적 모델을 제공하여, 현미경 이미지 (예: 투과 전자 현미경)와 정확하게 일치하는 식각 구조를 효율적으로 달성합니다.

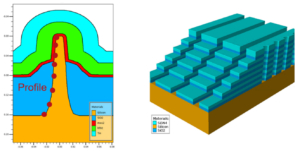

이번 시간에, FinFET 및 메모리 애플리케이션에서의 기하학적 식각 모델을 제시합니다. 핀의 형성, 비이상적 식각 프로파일 (휘어짐, 비틀림), 자체 정렬 공정 (멀티 패터닝)을 실현하는 기술을 설명합니다.

다음 사항을 살펴봅니다.

- 현미경 이미지에서 관찰된 정확한 식각 프로파일을 달성하는 방법

- 실바코의 Victory Process를 효율적으로 사용하여 FinFET 플로우에서 핀의 형상을 이루는 방법

- 메모리 애플리케이션 (3D NAND)의 트렌치와 컨택 홀에 기하학적 식각 모드를 적용하는 방법

- 실바코 Victory Process의 강력한 ETCH DRY, ETCH POLYLINE 명령어 사용 방법

발표

Alexander Toifl, 실바코 TCAD 개발 엔지니어

Alexander Toifl, 실바코 TCAD 개발 엔지니어

Alexander Toifl은 2021년 실바코에 입사한 이후 Victory Process의 식각 및 증착 모델을 담당하고 있습니다. 오스트리아 빈 공과대학(TU Wien)에서 마이크로 일렉트로닉스 및 광자학 석사 학위와 전기공학 박사 학위를 받았습니다.

참석 대상

TCAD 공정 플로우에서 식각 프로파일을 효율적으로 달성하기 위한 솔루션을 찾는 엔지니어 및 경영진

일시: 2022년 8월 12일

장소: 온라인

시각: 2:00am-2:30am (한국 시각)

언어: 영어