A CAD Framework for Co-Design and Analysis of CMOS-SET Hybrid Integrated Circuits

Introduction

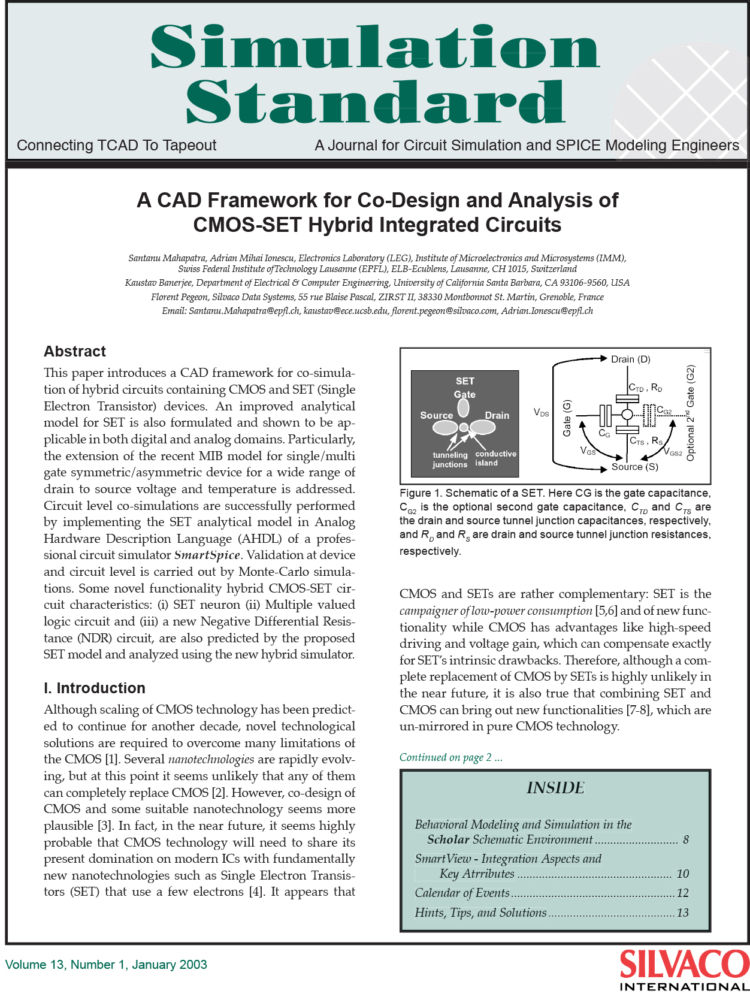

This paper introduces a CAD framework for co-simulation of hybrid circuits containing CMOS and SET (Single Electron Transistor) devices. An improved analytical model for SET is also formulated and shown to be applicable in both digital and analog domains. Particularly, the extension of the recent MIB model for single/multi gate symmetric/asymmetric device for a wide range of drain to source voltage and temperature is addressed. Circuit level co-simulations are successfully performed by implementing the SET analytical model in Analog Hardware Description Language (AHDL) of a professional circuit simulator SmartSpice. Validation at device and circuit level is carried out by Monte-Carlo simulations. Some novel functionality hybrid CMOS-SET circuit characteristics: (i) SET neuron (ii) Multiple valued logic circuit and (iii) a new Negative Differential Resistance (NDR) circuit, are also predicted by the proposed SET model and analyzed using the new hybrid simulator.