Managing the Complexity of FinFET Standard Cell Layout with Cello

配信開始日: 2022年2月17日

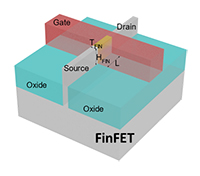

FinFETテクノロジは、MOSFETと比較して高密度化、高性能化、低消費電力化を実現することができます。しかし、その代償として設計はより一層複雑になります。悪影響を及ぼすレイアウト依存性が顕著になるだけでなく、デザイン・ルールもこれまで以上に複雑になります。デザイン・ルール違反の多くは、スタンダード・セルの広い領域にまたがり、複数のポリゴンを含むため、もはや局所的に修正することはできません。

FinFETテクノロジは、MOSFETと比較して高密度化、高性能化、低消費電力化を実現することができます。しかし、その代償として設計はより一層複雑になります。悪影響を及ぼすレイアウト依存性が顕著になるだけでなく、デザイン・ルールもこれまで以上に複雑になります。デザイン・ルール違反の多くは、スタンダード・セルの広い領域にまたがり、複数のポリゴンを含むため、もはや局所的に修正することはできません。

本ウェビナーでは、FinFET スタンダード・セルのレイアウト設計における課題をいくつか取り上げ、シルバコの Celloを使用して、これらの問題に対処する方法を説明します。

内容

- FinFETの概要と用途

- FinFETレイアウト設計

- FinFET設計と実装でのCelloの利用方法

プレゼンタ

シルバコのカリフォルニア州サンタクララに勤務するOsvaldo Martinello は、Foundation IP グループのSr. R&D Directorとして、IP 設計と最適化のツール開発を主導しています。ブラジル Porto AlegreのUFRGSでComputer Engineeringの学位と Computer Scienceの修士号を取得しています。

シルバコのカリフォルニア州サンタクララに勤務するOsvaldo Martinello は、Foundation IP グループのSr. R&D Directorとして、IP 設計と最適化のツール開発を主導しています。ブラジル Porto AlegreのUFRGSでComputer Engineeringの学位と Computer Scienceの修士号を取得しています。

対象:

IP、回路、CAD、SoCそしてシステム設計に携わるエンジニア、プロダクト・マネージャおよびエンジニアリング・マネージャ

[日本時間]

開催日: 2022年2月11日

配信: オンライン

開催時間: 3:00-3:30 JST

言語: 英語