독자적인 SmartSpice 4단자 TFT 모델로 TFT 기반 평면 패널 디자인을 개선

오늘날 업계의 수많은 TFT 기술은 4단자 소자를 기반으로 하고 있습니다. 이와 대조적으로, 타 벤더의 SPICE 시뮬레이터는 3단자 TFT 컴팩트 모델만 지원할 수 있습니다. 3단자 TFT 컴팩트 모델을 이용하여 4단자 TFT 소자를 모델링할 수도 있지만, 이상적인 상황과는 거리가 멀고 모델링 팀에 부담을 줄 수 있으며, 디자인 팀에 제약이 될 수 있습니다. FPD 기업도 자체적인 4단자 TFT 컴팩트 모델을 개발하고 CMI (Custom Model Interface) 기술을 활용하여 SPICE 수준에서 시뮬레이션할 수 있지만, 이를 위한 전문 지식과 리소스를 갖춘 기업은 거의 없습니다.

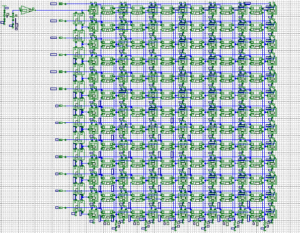

이번 시간에, SmartSpice의 4단자 TFT 컴팩트 모델에 대해 설명합니다. 업계에서 독자적으로, 이러한 컴팩트 모델의 몇 가지 특징과 이로 인해 모델링 팀과 디자인 팀 모두에게 제공되는 일단의 자유도를 제시합니다. 본 모델은 광범위한 분야에 적용할 수 있어, 비정질 실리콘, 폴리 실리콘, 유기물, 금속산화물 TFT, LTPS, LTPO, 플렉시블 디스플레이 기술 등 다양한 기술에 기초한 소자 시뮬레이션에 채택하였습니다. SmartSpice의 독자적인 4단자 TFT 모델을 활용하여, 다른 시뮬레이터에서 제공할 수 없는 방식으로 FPD 팀이 설계 품질을 개선할 수 있도록 도울 수 있습니다.

다음 사항을 살펴봅니다.

- 실바코 SmartSpice 4단자 TFT 컴팩트 모델의 개요

- 현실에서 4단자 TFT 컴팩트 모델을 사용하는 방법

- 다양한 디스플레이 기술 지원

- 전체 개발 생산성 및 정확성 향상

발표

Jody Matos 박사는 소프트웨어와 하드웨어 설계의 연구 개발에 열정적인 컴퓨터 공학 박사입니다. 실바코에서 회로 시뮬레이션 담당 이사로서, EDA 툴에 대한 R&D 및 비즈니스 관련 프로젝트를 관리하고 있습니다. 현재, 주로 아날로그, 디지털 및 믹스드 시그널 IC 설계에 대한 회로 시뮬레이션 및 분석에 관련된 업무를 맡고 있습니다.

Jody Matos 박사는 소프트웨어와 하드웨어 설계의 연구 개발에 열정적인 컴퓨터 공학 박사입니다. 실바코에서 회로 시뮬레이션 담당 이사로서, EDA 툴에 대한 R&D 및 비즈니스 관련 프로젝트를 관리하고 있습니다. 현재, 주로 아날로그, 디지털 및 믹스드 시그널 IC 설계에 대한 회로 시뮬레이션 및 분석에 관련된 업무를 맡고 있습니다.

Matos 박사는 브라질의 Federal do Rio Grande do Sul (UFRGS)에서 마이크로 전자공학 석사 및 컴퓨터 공학 박사 학위를 받았습니다. 컴퓨터 과학과 마이크로 전자 공학에 대한 30개 이상의 연구 논문과 특허 출원을 공동 저술하였습니다. 또한, 저명한 저널의 기술 위원회 및 설계 자동화 분야의 다양한 국제 회의에 전문가로 참여하였습니다.

참석 대상

디스플레이 설계자, 아날로그 회로 설계자, CAD 및 SoC 설계 엔지니어, 회로 시뮬레이션 분야의 제품 관리자 및 엔지니어링 관리자, 회로 시뮬레이션에 입문한 학생.

일시: 2022년 4월 29일

장소: 온라인

시각: 2:00am-2:30am (한국 시각)

언어: 영어