STMicroelectronics, SiC 소자의 단락 현상에 대한 표면 결함 점의 영향 분석에 실바코 TCAD 활용

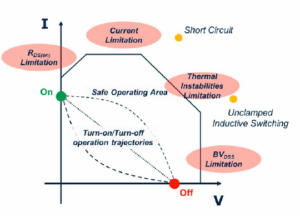

SiC 소자의 스위칭 동작 중에, 소자가 과부하 비정상 상태에 도달할 수 있으므로, 일부 애플케이션에서는 강력한 사양이 필요합니다 (예: 단락 회로 및 UIS 테스트). 믹스드 모드 회로에서 이러한 현상을 시뮬레이션할 수 있으며, 시뮬레이션과 실험 정보를 교환하여 시뮬레이션 파라미터의 정확한 튜닝을 통해 동적 단계에서 전기 열의 움직임을 예측할 수 있습니다. 단락 회로의 현상에 대한 연구를 예시로 살펴봅니다. 실바코의 TCAD 시뮬레이션으로 활성 영역에 한정된 결함의 단락 회로에 대한 영향을 연구하였습니다. 평평한 인터페이스 바디/드레인, 채널 영역의 SiC/산화물 인터페이스, 곡선 인터페이스 바디/드레인에 한정된 결함 점에 대해 다양한 사례를 연구하였습니다. 위치에 대한 민감도도 살펴봅니다.

SiC 소자의 스위칭 동작 중에, 소자가 과부하 비정상 상태에 도달할 수 있으므로, 일부 애플케이션에서는 강력한 사양이 필요합니다 (예: 단락 회로 및 UIS 테스트). 믹스드 모드 회로에서 이러한 현상을 시뮬레이션할 수 있으며, 시뮬레이션과 실험 정보를 교환하여 시뮬레이션 파라미터의 정확한 튜닝을 통해 동적 단계에서 전기 열의 움직임을 예측할 수 있습니다. 단락 회로의 현상에 대한 연구를 예시로 살펴봅니다. 실바코의 TCAD 시뮬레이션으로 활성 영역에 한정된 결함의 단락 회로에 대한 영향을 연구하였습니다. 평평한 인터페이스 바디/드레인, 채널 영역의 SiC/산화물 인터페이스, 곡선 인터페이스 바디/드레인에 한정된 결함 점에 대해 다양한 사례를 연구하였습니다. 위치에 대한 민감도도 살펴봅니다.

다음 사항을 살펴봅니다.

- WBG (Wide Band Gap) 기술 및 SiC의 주요 특징

- SiC MOSFET 스위칭 동작 및 견고함

- TCAD 시뮬레이션 및 소자 신뢰성

- 단락 회로: 표면 결함 점의 충격

발표

Salvatore Cascino, SiC R&D 엔지니어, ST Microelectronics

Salvatore Cascino는 1970년 이탈리아 팔레르모에서 태어났으며, 팔레르모 대학에서 물리학 학위를 취득했습니다. 파도바의 핵융합부 (FTU 프로젝트)와 융합 연구 그룹 (RFX 프로젝트)으로 ENEA (프라스카티-로마)에 참여했습니다. 현재 ST Microelectronics (카타니아)에서 연구 개발 그룹에 참여하고 있으며, 실리콘 카바이드 소자를 위한 기술 개발에도 관심을 두고 있습니다. 그는 감지 애플리케이션과 무선 주파수 소자 개발에도 참여한 적이 있습니다.

참석 대상

반도체 소자 및 공정 엔지니어, 제품 관리자, 엔지니어링 관리자

일정 (한국 시각)

3월 28일 11:00 AM

3월 28일 7:00 PM

3월 29일 2:00 AM