Parasitic Capacitance Extraction with Hipex and Exact

Overview

To extract parasitic capacitances from a circuit layout, you need to perform the following steps:

- Define the technology process and material data. This includes vertical order of mask layers and dielectrics, their thicknesses, conductivity, and permittivity constants.

- Use the technology data as input to a 2D or 3D field solver to obtain capacitance coefficients.

- Generate a rule file for a full-chip capacitance extractor using the obtained capacitance coefficients.

- Run the capacitance extractor using the generated rule file.

Silvaco provides tools for performing all the steps above. You can use EXACT for steps from 1 to 3 and HIPEX-C for step 4.

EXACT is a 3D field solver powered by a 3D process simulator to accurately represent the cross-sections in the physical chip, rather than using square cross-sections. This maximizes the accuracy of the capacitance coefficients because the calculated capacitance is derived from realistic cross-sections and 3D shapes. See [1] for more information.

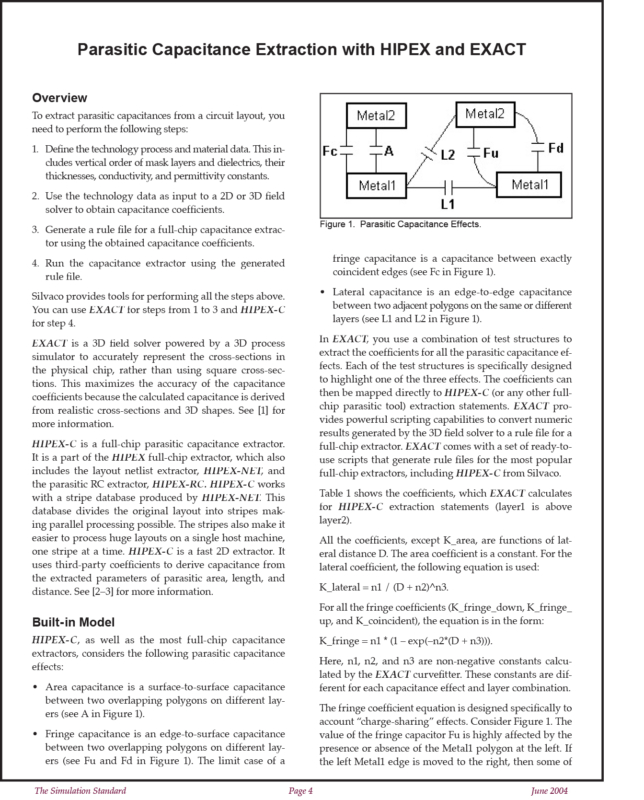

HIPEX-C is a full-chip parasitic capacitance extractor. It is a part of the HIPEX full-chip extractor, which also includes the layout netlist extractor, HIPEX-NET, and the parasitic RC extractor, HIPEX-RC. HIPEX-C works with a stripe database produced by HIPEX-NET. This database divides the original layout into stripes making parallel processing possible. The stripes also make it easier to process huge layouts on a single host machine, one stripe at a time. HIPEX-C is a fast 2D extractor. It uses third-party coefficients to derive capacitance from the extracted parameters of parasitic area, length, and distance. See [2–3] for more information.