Non-Stationary Transport Effects: Impact on Performances of Realistic 50nm MOSFET Technology

Abstract

We analyze quantitatively the real impact of technology on the needed level for carrier transport modeling. The results, based on theoretical analyzes, are applied to existing devices. This work shows which recipes must be used to evaluate the performances of advanced device architectures (down to 50nm gate length). An original point of this work is the investigation of technology influence (channel doping and LDD doping) on injection velocity at source side and on drain current. The results open the perspective of specific engineering of access regions in order to take full advantage of non-stationary effects on the drain current.

Introduction

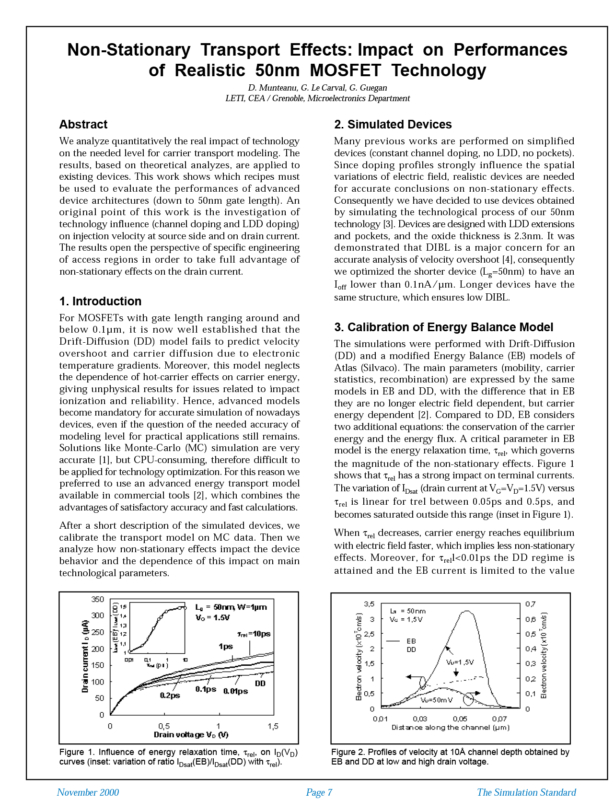

For MOSFETs with gate length ranging around and below 0.1µm, it is now well established that the Drift-Diffusion (DD) model fails to predict velocity overshoot and carrier diffusion due to electronic temperature gradients. Moreover, this model neglects the dependence of hot-carrier effects on carrier energy, giving unphysical results for issues related to impact ionization and reliability. Hence, advanced models become mandatory for accurate simulation of nowadays devices, even if the question of the needed accuracy of modeling level for practical applications still remains. Solutions like Monte-Carlo (MC) simulation are very accurate [1], but CPU-consuming, therefore difficult to be applied for technology optimization. For this reason we preferred to use an advanced energy transport model available in commercial tools [2], which combines the advantages of satisfactory accuracy and fast calculations.

After a short description of the simulated devices, we calibrate the transport model on MC data. Then we analyze how non-stationary effects impact the device behavior and the dependence of this impact on main technological parameters.

Simulated Devices

Many previous works are performed on simplified devices (constant channel doping, no LDD, no pockets). Since doping profiles strongly influence the spatial variations of electric field, realistic devices are needed for accurate conclusions on non-stationary effects. Consequently we have decided to use devices obtained by simulating the technological process of our 50nm technology [3]. Devices are designed with LDD extensions and pockets, and the oxide thickness is 2.3nm. It was demonstrated that DIBL is a major concern for an accurate analysis of velocity overshoot [4], consequently we optimized the shorter device (Lg=50nm) to have an Ioff lower than 0.1nA/µm. Longer devices have the same structure, which ensures low DIBL.