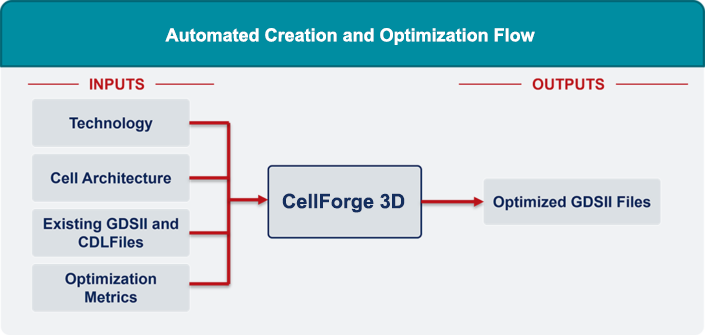

CellForge 3D Flow

특징

- 10nm 이하 FinFET 지원

- P&R 엔진을 포함하여, 구성 레이아웃에 따라 정확하게 생성

- 멀티 패턴 규칙, 컷 규칙 및 기타 복잡한 FinFET 공정 규칙과 호환

- 구문에 민감한 간격 및 인클로저 규칙, 선호하는 모양 패턴, 자체 정렬 이중 패턴 (SADP) 및 로컬 인터커넥트 지원 등의 최신 공정 기술 포함

- 확장할 수 있는 병렬 처리를 통해 처리량 향상

- 여러 레이아웃 옵션을 동시에 생성

- 타사의 DRC, LVS, LPE 툴과 연계하여 고품질 사인오프 레이아웃을 제공하며, 기존 플로우에 대한 중단을 최소화

- 공정 기술 및 파운드리 설계 규칙을 유연하게 설정하여, 신속하게 DRC 무결점 레이아웃 생성 가능

장점

- 생산성의 대폭 향상

- 레이아웃에서 수작업을 제거 또는 대폭 감축

- 작업 시간 단축, 하루 만에 라이브러리 완성

- 다양한 기준으로 탐색 가능 (셀 아키텍처, 설계 규칙, 크기 조정, 상이한 트랙 높이, DFM 규칙)

- 일관적인 레이아웃

- 스키매틱을 재사용하여 설계 시간 단축

- PDK 업데이트 자동화